[TOC]

语言学习

[1]java速成^1

Jdk(包含jre、开发工具和基础类库)、jre、jvm(运行.class核心,跨平台)三者包含关系;

javac ~.java-> 编译生成.class字节码文件 ->java ~.class运行;四种语句结构:顺序、选择、循环、异常处理

面向对象三大特征:封装、继承、多态

Java基本语法:

类格式:

1

2

3[修饰符] class 类名 [extends 父类名] [implements 接口名] {

//类体,包括类的成员和成员方法

}方法格式:

1

2

3

4权限修饰符 返回值声明 方法名称(参数列表){

方法中封装的逻辑功能;

return 返回值;

}权限:

public、protected、default、private四级,对应到“类内部、本包、子类、外部包”的阶梯权限图关键字(系统占用的关键词)、标识符(自己定义的)

变量

基本数据类型(4整型、2浮点、char、boolean)【float a=1.1f(不加默认double)、long b=1l、char c=’你’】、引用数据类型(string、数组、接口、类);局部变量(方法/语句块内部定义)、成员变量(方法外,类内定义);常量final int a=3;

自动类型转换(小到大)、强制类型转换(大到小,加转换符)

运算符:同c语言

语句:if、switch、while、for等与c语言一样,但java的for循环数组遍历可以有类似python写法

数组:声明;动、静态初始化;常见操作(数组长度

a.length;数组遍历;拷贝Arrays.copyOf(T[] original,int newLength );排序Array.sort(arr);转字符串Array.toString(arr))输入(实例化后调用):

Scanner sc=new Scanner(System.in);int e=sc.nextInt();输出:

System.out.println()【或print()】;System.out.printf()和c语言一样格式化输出类与对象

通过权限关键字对属性和方法封装(一般让类内属性不能直接访问,通过方法get、set等间接访问;通过”new 关键字”进行实例化)【方法内通过”this.属性”访问属性】;继承extends

基类Object及其方法(万物父类,其他默认”extends Object”)

子类中方法若与父类相同则重写方法【完全一样,且子类的权限需高于父类】

封装步骤:修改属性的可见范围(private);创建set、get方法访问属性(可加入对写入合法性判断)

构造方法:在创建对象(new)时初始化对象,与类同名的public方法,进行一系列初始操作,可传参。

方法的重载【区别于子类中方法的重写】:在同一类中;相同方法名;参数列表必须不同

this关键字:非静态方法中(无static修饰),意会;super关键字:调用父类的属性和方法

static关键字:被修饰成为静态变量/方法,不需new可直接调用;static{ ;}静态代码块(调用自动加载,初始化)

final关键字:修饰的类不能被继承,修饰的方法不能被重写,修饰的变量(引用变量是其地址)不能被改变

抽象方法(不需写逻辑语句) 、抽象类(有抽象语句的不能被继承,除非在子类里被实现)

接口interface(替换class):内所有方法都是抽象的(交给子类实现【默认为public abstract,可省略】),变量只能为public static final类型(可省略);在实现的子类名后加implements 父类名;接口可被多实现

[2] Scala速成[^2]

Scala 的编译模型(独立编译,动态类加载)与 Java 和 C# 一样,所以 Scala 代码可以调用 Java 类库;面向对象特质(与java一样);函数式编程(函数可做参数、模式匹配、闭包);类型系统;并发性、拓展性…

scalac HelloWorld.scala // 把源码编译为字节码scala HelloWorld // 把字节码放到虚拟机中解释运行基本语法:区分大小写;类名单词的每个第一个字母大写,方法的第一个字母小写;

def main(args: Array[String])——Scala程序从main()方法开始处理,这是每一个Scala程序的强制程序入口部分;转义标志符(eg.

:->使用$colon$minus$greater)、混合标志符(字符数字后面跟着一个或多个符号)、字面量标志符(使用”定义的字符串)、在’’之间使用任何有效的 Scala 标志符(声明非保留关键字,eg.Thread.`yield`())scala包:package定义包(可使用大括号定义多个包[class])、impor引用包

1

2package com.runoob

class HelloWorld1

2

3package com.runoob {

class HelloWorld

}1

2

3

4

5

6

7import java.awt.Color // 引入Color

import java.awt._ // 引入包内所有成员

def handler(evt: event.ActionEvent) { // java.awt.event.ActionEvent

... // 因为引入了java.awt,所以可以省去前面的部分

}1

2

3

4

5

6

7

8import java.awt.{Color, Font}

// 重命名成员

import java.util.{HashMap => JavaHashMap}

// 隐藏成员

import java.util.{HashMap => _, _} // 引入了util包的所有成员,但是HashMap被隐藏了默认情况下,Scala 总会引入 java.lang._ 、 scala._ 和 Predef._,所以以scala开头的包,使用都是省去scala.的。

Scala数据类型:java数据类型加大量集合类型、特殊类型;且所有数据类型都是对象(无java原生类型概念),故可在类型上调用方法

[3] Chisel速成

1. VS Code环境配置[^3]

下载插件;scala换国内源;安装SBT:参考Chisel入门——在windows下vscode搭建|部署Scala2.13.3开发环境|用Chisel点亮FPGA小灯等实验_vscode scala-CSDN博客

ubuntu上安装sbt: Chisel+VS Code+Ubuntu/WSL2开发环境搭建与使用

1 | sudo apt install default-jre |

2. Chisel-Chip示例工程的使用

README文件阅读——这是一个chisel工程模版

在工程根目录(实测是~/project)运行

sbt test判断是否能工作其他推荐阅读:sbt Reference Manual — sbt Reference Manual

命名规则: Naming Conventions | Style Guide | Scala Documentation

一般来说,Scala 使用“驼峰式”命名法。也就是说,除了可能的第一个单词外,每个单词的首字母都大写(缩略词视为普通词汇);避免使用下划线;class名和object名使用大驼峰命名法(一个例外是模仿包或函数的对象,这种情况并不常见);package名遵循java写法;method方法名遵循小驼峰命名(def…,首字母小写);常量也使用大驼峰命名法,值val和变量名var应采用小驼峰命名法:

对于简单的类型参数,应使用单个大写字母,从A开始;或使用助记字母(这与Java从T开始的惯例不同);如果类型参数具有更具体的含义,应按照类命名规范使用描述性名称(而非全大写风格),例如:

1

2

3

4

5

6

7

8

9

10

11class List[A] {

def map[B](f: A => B): List[B] = ...

}

class Map[Key, Value] {

def get(key: Key): Value

def put(key: Key, value: Value): Unit

}

class Map[K, V] {

def get(key: K): V

def put(key: K, value: V): Unit

}文件结构

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19src/

main/

resources/

<files to include in main jar here>

scala/

<main Scala sources>

scala-2.12/

<main Scala 2.12 specific sources>

java/

<main Java sources>

test/

resources

<files to include in test jar here>

scala/

<test Scala sources>

scala-2.12/

<test Scala 2.12 specific sources>

java/

<test Java sources>sbt build definition files:

build.sbt常用sbt命令

1

2

3sbt run

sbt "testOnly cpu.CPUTest"

sbt "testOnly cpu.CPUTest -- -DwriteVcd=1"

clean删除所有生成的文件 (在 target目录下)。compile编译源文件(在 src/main/scala和src/main/java目录下)。test编译和运行所有测试。 console进入到一个包含所有编译的文件和所有依赖的 classpath 的 Scala 解析器。输入 :quit, Ctrl+D (Unix),或者 Ctrl+Z (Windows) 返回到 sbt。run <参数>*在和 sbt 所处的同一个虚拟机上执行项目的 main class。【包括编译Verilog】 package将 src/main/resources下的文件和src/main/scala以及src/main/java中编译出来的 class 文件打包成一个 jar 文件。help <命令>显示指定的命令的详细帮助信息。如果没有指定命令,会显示所有命令的简介。 reload重新加载构建定义( build.sbt,project/*.scala,project/*.sbt这些文件中定义的内容)。在修改了构建定义文件之后需要重新加载。编写自己的文件

删除自带的示例文件:

src/main/scala/GCD; src/test/scala/GCD,在src/main/scala下创建文件夹编写源代码-

对电路进行测试需要包含至少两部分,一个是DUT(待测件),另一个是测试逻辑,也叫testbench 。DUT从AnyFlatSpec和ChiselScalatestTester拓展来的,因此是具有ChiselTest功能的ScalaTest。而调用test()方法时,以新创建的DUT的一个实例为参数,以测试代码为函数字面量(function literal)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15class SimpleTest extends AnyFlatSpec with ChiselScalatestTester {

"DUT" should "pass" in {

test(new DeviceUnderTest) { dut =>

dut.io.a.poke(0.U)

dut.io.b.poke(1.U)

dut.clock.step()

println("Result is: " + dut.io.out.peek().toString)

dut.io.a.poke(3.U)

dut.io.b.poke(2.U)

dut.clock.step()

println("Result is: " + dut.io.out.peek().toString)

}

}

}在端口上***调用

poke来给端口赋值,它接受的是端口对应的Chisel类型的值。而在输出端口上调用peek可以把端口的输出给读取出来,返回值也是该端口对应的Chisel类型的值;测试中调用dut.clock.step()可以让时钟前进一个周期,以此让仿真前进。要是想要前进多个周期,我们可以给step()提供一个参数; 可以通过在输出端口上调用expect(value)***来在testbench中给出预期值- 在sbt参数中加入

-- -DwriteVcd=1以生成波形vcd文件;或在代码中加入printf输出每个时钟的信号

- 在sbt参数中加入

生成Verilog代码

在要生成Verilog的模块文件内添加以下代码:创建了一个新的

Hello对象,然后传递给Chisel的emitVerilog()函数,它会生成Hello模块对应的Verilog文件Hello.v。第二个参数类型是字符串的数组 ,指定生成位置。最后运行sbt run,若有多个创建对象会在终端询问具体要创建哪个1

2

3object HelloOption extends App {

emitVerilog(new Hello(), Array("--target-dir", "generated"))

}在线Scala开发环境 : Scastie

Chisel的工具流 :生成

*.v,*.fir文件和*.anno.json

3. riscv-tests开源测试包的使用

课程学习

[1]哈工大RISC-V SoC Verilog vivado

1.SoC仿真

2.取值译码单元(IF、ID)设计

3.控制单元实现

完整数据通路:

4.基于trace验证cpu方法

5.总线、IO设计及上板验证

6.流水线设计

[2]“一生一芯”

一、 设备和输入输出

- AM——抽象接口,针对MMIO(Memory-mapped I/O,统一编址)和PMIO(port-mapped I/O,独立编址)

- 常用外设——GPIO、串口、时钟、键盘、显卡

- 实现方法——总线协议+设备控制器

二、总线

- Decoupled创建简单握手连接

- 采用自定义定义函数进行处理器模式选择

- AXI4总线的原理、总线仲裁器(Arbiter)

- crossbar(Xbar),Xbar和Arbiter可合并成多进多出Xbar,也称Interconnect,总线桥等

- RISCV内存访问检查机制

图书阅读

[1] 敏捷硬件开发语言 Chisel 与数字系统设计[^4]

第一、二章

Scala语言是什么:基于JVM(JAVA虚拟机),兼容现有JAVA程序,较JAVA更简洁调;面向对象(封装,继承,多态)

Chisel语言是什么:(Constructing Hardware in Scala Embedded Language)Chisel是DSL[领域专用语言],以scala为宿主

Verilog HDL发展方向:改进派,即system Verilog;使用软件语言描述(system C 和 Chisel)【按顺序执行,区别与Verilog和VHDL!】

Scala解释器的下载及使用(cmd);Intellij IDEA的使用和scala工程创建

scala脚本:以一个可以计算出结果的表达式或由副作用的函数结尾[scala运行];非~:以定义结尾(class、object,package…)[scalac运行]

Linux上chisel开发环境搭建

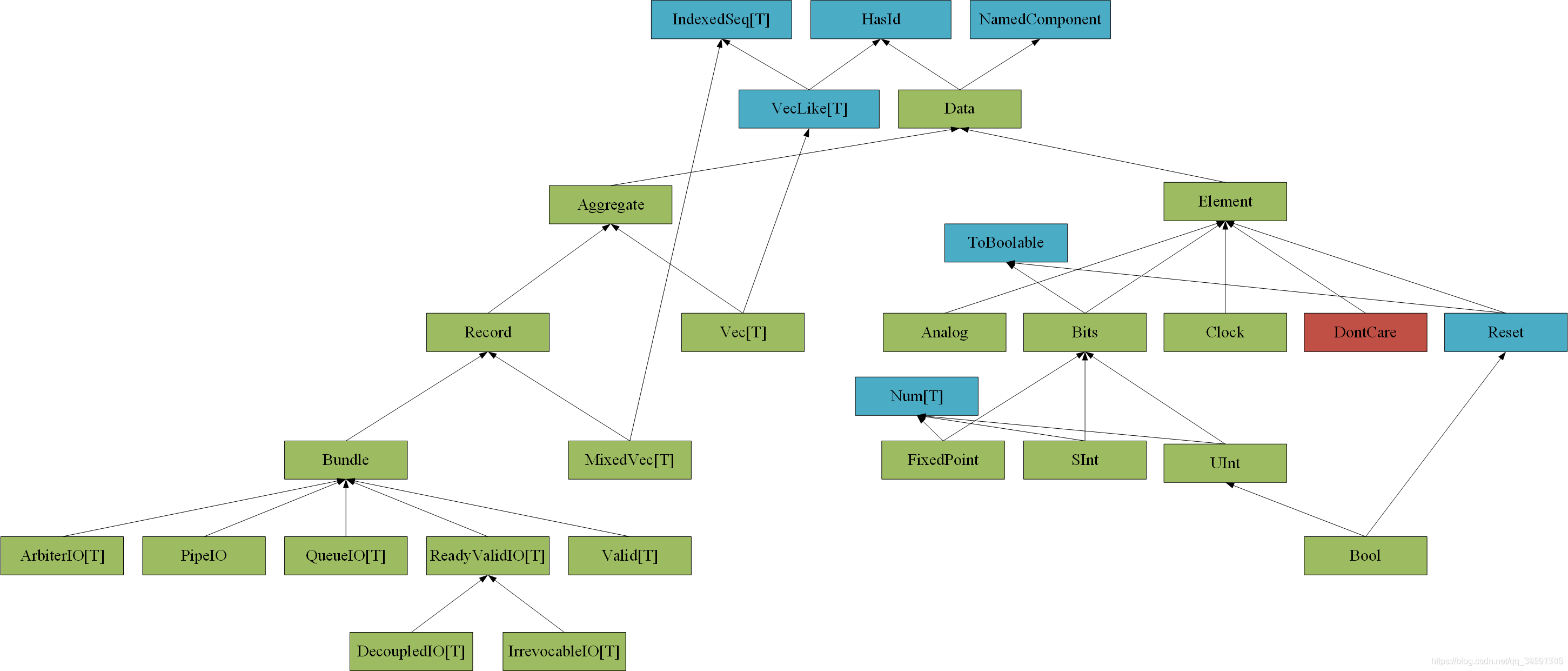

Chisel数据类型:

注:1.chisel目前不支持Verilog的四态逻辑里的x和z(只有芯片对外I/O处才能出现三态门,内部设计几乎用不到)

数据字面量与数据类型

在 Chisel 里,因为硬件电路的不可变性,所有对象都应该由 val 类型的变量来引用,输出端口在定义时使用“=”与端口变量名进行绑定 ;

数据字面量指的是代码中“=”右边的值,在scala中通过一系列隐式类:

fromIntToLiteral、fromBigIntToLiteral、fromStringToLiteral等中的U、S、asUInt(类型转换)等方法来构造对应类型的对象。例如:fromStringToLiteral(“b01_01”).U数据宽度:

U、S等方法可以带参数列表def U(width: Width): [UInt],其中Width类型同Int,使用隐式类fromIntToWidth的方法W返回Width对象注:若不使用W方法,则

1.U(32)表示取“1”的第32位;Bool类型固定位1位宽,若使用类型转换,如asBools(8)则得到Bool类型序列Seq[Bool];Bool类有asClock方法,Clock只有一个方法asUINnt使用

final macro def apply(x: Int, y: Int): UInt方法,返回此UInt中从高位x到低位y(包括两端)的位子集,静态寻址。使用类型转换实现子类赋值:将UInt通过

asBools转化成seq[Bool],配合VecInit构成向量,便可对指定位进行赋值,最后在使用asUInt转化回来:1

2

3

4

5

6

7

8

9

10

11class TestModule extends Module {

val io = IO(new Bundle {

val in = Input(UInt(10.W))

val bit = Input(Bool())

val out = Output(UInt(10.W))

})

val bools = VecInit(io.in.asBools)

bools(0) := io.bit

io.out := bools.asUInt

}向量

可使用scala内建数组、列表、集等数据结构或chisel专属的Vec[T],其伴生对象有一个apply工厂方法VecFactory构建:eg.

val myVec = wire(vec(3,UInt(32.W)));以及另一个工厂方法

VecInit[T],通过接收一个Seq[T](这里的Seq包括seq、array、list、tuple、queue等集合)作为参数来构造向量,或者是多个重复参数 , 这个工厂方法常把有字面值的数据作为参数, 一般用于初始化Reg组、ROM、RAM等1

2

3

4val Vec1 = VecInit(1.U, 2.U, 3.U, 4.U)//重复参数

val Vec2 = VecInit(Seq.fill(8)(0.U(8.W)))//序列

val reg1 = RegNext(VecInit(io.a, io.a), VecInit(0.U, 0.U))

val reg2 = RegInit(VecInit(0.U(8.W), 0.U(8.W)))混合向量MixedVec

抽象类Bundle

类似C语言中结构体(struct),可编写一个自定义类继承它,里面包含其他Data类型字段,用于协助构建线网或寄存器,构建一个模块的端口列表,或者一部分端口:

1 | class TestModule extends Module { |

Bundle可以与UInt进行互换,其中的方法asUInt可以将Bundle内含的字段拼接,并且前面的字段在高位(类似Verilog拼接赋值):

1 | class MyBundle extends Bundle { |

内建操作符

总结:常用

UInt、SInt、Bool、Bundle、Vec[T]

第三章 模块与硬件类型

最基本硬件类型:IO、Wire、Reg;硬件类型与数据类型的区分;定义电路的类均继承自Module类

赋值

使用Val 类型变量,使用“=”与端口变量绑定,进行初始化;后续使用“:=”进行赋值

端口

IO[T<:Data](iodef:T);定义端口,且字段只能是io,参数为bundle类型对象Input[T<:Data](source:T)/Output[T<:Data](source:T)表明方向,参数传数据类型注:

- chisel还不支持inout双向端口,从性质上端口仍是线网

- 对于简单端口可使一个继承自Bundle的匿名类“

new Bundle{...}”,但对于较大的公共接口,应单独写成具名的Bundle子类方便修改。

1

2

3

4

5val io=IO(new Bundle{

val in=Input(Vec(8,UInt(8.W)))

val sel=Input(UInt(3.W))

val out=Output(UInt(8.W))

})1

2

3

4

5

6

7

8

9class MyIO extends Bundle {

val in = Input(Vec(5, UInt(32.W)))

val out = Output(UInt(32.W))

}

class MyModule extends Module {

val io = IO(new MyIO) // 模块的端口列表

...

}翻转端口列表方向

Flipped()(避免大量同名但是方向相反要重写)1

2

3

4class MyModule_2 extends Module {

val io = IO(Flipped(new MyIO)) // out是输入,in是输出

...

}整体连接

<>(用于父子模块端口同向连通或同级同名反向端口连接)1

2

3

4

5

6

7

8

9

10class MyModule extends Module {

val io = IO(new Bundle {

val x = new MyIO

val y = Flipped(new MyIO)

val supX = new MyIO

})

io.x <> io.y //相当于io.y.in:=io.x.in;io.x.out:=io.y.out

val sub = Module(new MySubModule)

io.supX <> sub.io.sbuX //相当于sub.io.sbuX.in:=io.supX.in;io.supX.out:=sub.io.sbuX.out

}动态修改端口

通过引入scala的Boolean参数、可选值及if语句创建;或使用

Zero-Width(位宽为0不生成):1

2

3

4

5

6

7

8

9

10

11

12class HalfFullAdder(val hasCarry: Boolean) extends Module {

val io = IO(new Bundle {

val a = Input(UInt(1.W))

val b = Input(UInt(1.W))

val carryIn = Input(if (hasCarry) UInt(1.W) else UInt(0.W))

val s = Output(UInt(1.W))

val carryOut = Output(UInt(1.W))

})

val sum = io.a +& io.b +& io.carryIn

io.s := sum(0)

io.carryOut := sum(1)

}

模块

(继承关系:LegacyModule(Module) < MultiIOModule < RawModule)

Module: 默认生成clock和reset,必须实现抽象成员io

MultiIOModule: 默认生成clock和reset,无抽象成员io,根据需要定义IO

RawModule: 默认不生成时钟和复位,在需要特定时钟或复位命名约定的设计匹配时特别有用,根据需要定义IO,无抽象成员io

1

2

3

4

5

6class add extend MultiIOModule {

val a = IO(Input(UInt(1.W)))

val b = IO(Input(UInt(1.W)))

val c = IO(Output(UInt(2.W)))

out c := io.a + io.b

}定义模块:一般通过继承Module类实现,具备以下特点

继承自Module类

包含一个用于接口的抽象类”io”,且必须引用端口对象(即有

val io = IO(...))在类的主构造器里进行内部电路连线(即在类里面有相关构造内容【

:=,<>和一些控制结构等】)

例化模块(使用

new生成一个实例对象并传递给单例对象Module的apply方法)val m1 = Module(new Mux2)批量例化:利用向量的工厂方法

VecInit[T<:Data](模块的“io”字段是Bundle类型,是参数“Data”子类;实际电路连线只需针对模块端口),一般调用单例对象Seq的fill方法生成io序列1

2

3

4

5

6val m = VecInit(Seq.fill(3)(Module(new Mux2).io))

// 例化了三个Mux2,并且参数是端口字段io

m(0).sel := io.sel(0) // 模块的端口通过下标索引,并且路径中没有“io”

m(0).in0 := io.in0

m(0).in1 := io.in1

...

线网

(电路节点,类似VHDL的

signal和Verilog的wire)——通过工厂方法Wire[T<:Data]赋值1

2

3val myNode = Wire(UInt(8.W))

myNode := 0.U;

myNode := io.in + 1.U;//Scala作为软件语言顺序执行,定义具有覆盖性1

2

3

4

5

6

7

8val w0 = Wire(UInt()) // width is inferred 若不提供位宽,代码将自动推断

val w1 = Wire(UInt(8.W)) // width is set to 8

val w2 = Wire(Vec(4, UInt())) // width is inferred

val w3 = Wire(Vec(4, UInt(8.W))) // width of each element is set to 8

class MyBundle {

val unknown = UInt()

val known = UInt(8.W)

}WireDefault——构建有默认连接的线网( 信号有默认值,增加电路的可靠性和可维护性)【单/双参数两种形式】

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19// Literal chisel3.Bits initializer: width will be set to match

val w1 = WireDefault(1.U) // width will be inferred to be 1 ,即默认值为1

val w2 = WireDefault(1.U(8.W)) // width is set to 8 ,即默认值为11111111

//Non-Literal Element initializer - width will be inferred

val x = Wire(UInt())

val y = Wire(UInt(8.W))

val w1 = WireDefault(x) // width will be inferred

val w2 = WireDefault(y) // width will be inferred

//Aggregate initializer - width will be set to match the aggregate

class MyBundle {

val unknown = UInt()

val known = UInt(8.W)

}

val w1 = Wire(new MyBundle)

val w2 = WireDefault(w1)

// Width of w2.unknown is inferred

// Width of w2.known is set to 8未驱动的线网:如果在设计中故意为之,可赋值

Dontcare(全0,甚至把逻辑全优化掉)1

2

3

4val io = IO(new Bundle {

val outs = Output(Vec(10, Bool()))

})

io.outs <> DontCare

寄存器

普通寄存器

Reg[T<:Data](t:T)的赋值和Wire类似,可在when语句中用全局reset信号进行同步复位(要用asBool()将Reset类型转换)RegNext[T<:Data](next:T)——一般用于构造延迟一个周期的信号1

2

3val foo = Reg(UInt(4.W)) // width is 4

val bar = Reg(chiselTypeOf(foo)) // width is 4

bar := foo另一个工厂方法

RegNext[T<:Data](next:T,init:T)可以复位到制定值;使用RegNext实现输入信号的1、2周期延时:

1

2

3

4

5

6

7

8

9class lay extends Module {

val io = IO(new Bundle {

val a = Input(UInt(1.W))

val c1 = Output(UInt(1.W))

val c2 = Output(UInt(1.W))

})

io.c1 := RegNext(io.a,0.U)

io.c2 := RegNext(io.c1,0.U)

}实现8bit计数器:

1

2

3

4

5

6class counter extends Module {

val io = IO(new Bundle {

val out = Output(UInt(3.W))

})

io.out := RegNext(io.out + 1.U, 0.U)

}RegInt[T<:Data](init:T)——复位时被设置为初始值(类似WireDefault)【单/双参数形式】1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19//Literal chisel3.Bits initializer: width will be set to match

val r1 = RegInit(1.U) // width will be inferred to be 1

val r2 = RegInit(1.U(8.W)) // width is set to 8

//Non-Literal Element initializer - width will be inferred

val x = Wire(UInt())

val y = Wire(UInt(8.W))

val r1 = RegInit(x) // width will be inferred

val r2 = RegInit(y) // width will be inferred

//Aggregate initializer - width will be set to match the aggregate

class MyBundle extends Bundle {

val unknown = UInt()

val known = UInt(8.W)

}

val w1 = Reg(new MyBundle)

val w2 = RegInit(w1)

// Width of w2.unknown is inferred

// Width of w2.known is set to 8util包中的RegEnable——构建一个带使能端的寄存器1

2val regWithEnable = RegEnable(nextVal, ena)

val regWithEnableAndReset = RegEnable(nextVal, 0.U, ena)util包中的ShiftRegister[T<:Data](in:T,n:Int,resetData:T,en)——移位寄存器1

2val regDelayTwo = ShiftRegister(nextVal, 2, ena)

val regDelayTwoReset = ShiftRegister(nextVal, 2, 0.U, ena)例子(多个寄存器)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28import chisel3._

import chisel3.util._

class REG extends Module {

val io = IO(new Bundle {

val a = Input(UInt(8.W))

val en = Input(Bool())

val c = Output(UInt(1.W))

})

val reg0 = RegNext(io.a)

val reg1 = RegNext(io.a, 0.U)

val reg2 = RegInit(0.U(8.W))

val reg3 = Reg(UInt(8.W))

val reg4 = Reg(UInt(8.W))

val reg5 = RegEnable(io.a + 1.U, 0.U, io.en)

val reg6 = RegEnable(io.a - 1.U, io.en)

val reg7 = ShiftRegister(io.a, 3, 0.U, io.en)

val reg8 = ShiftRegister(io.a, 3, io.en)

reg2 := io.a.andR

reg3 := io.a.orR

when(reset.asBool) {

reg4 := 0.U

}.otherwise {

reg4 := 1.U

}

io.c := reg0(0) & reg1(0) & reg2(0) & reg3(0) & reg4(0) & reg5(0) & reg6(0) & reg7(0) & reg8(0)

}异步寄存器(异步时钟、复位)——使用

withClockAndReset或withClock或withReset构造寄存器组——通过

Vec[T]和VecInit1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30class REG2 extends Module {

val io = IO(new Bundle {

val a = Input(UInt(8.W))

val en = Input(Bool())

val c = Output(UInt(1.W))

})

val reg0 = RegNext(VecInit(io.a, io.a))

val reg1 = RegNext(VecInit(io.a, io.a), VecInit(0.U, 0.U))

val reg2 = RegInit(VecInit(0.U(8.W), 0.U(8.W)))

val reg3 = Reg(Vec(2, UInt(8.W)))

val reg4 = Reg(Vec(2, UInt(8.W)))

val reg5 = RegEnable(VecInit(io.a + 1.U, io.a + 1.U), VecInit(0.U(8.W),

0.U(8.W)), io.en)

val reg6 = RegEnable(VecInit(io.a - 1.U, io.a - 1.U), io.en)

val reg7 = ShiftRegister(VecInit(io.a, io.a), 3, VecInit(0.U(8.W), 0.U(8.W)), io.en)

val reg8 = ShiftRegister(VecInit(io.a, io.a), 3, io.en)

reg2(0) := io.a.andR

reg2(1) := io.a.andR

reg3(0) := io.a.orR

reg3(1) := io.a.orR

when(reset.asBool) {

reg4(0) := 0.U

reg4(1) := 0.U

}.otherwise {

reg4(0) := 1.U

reg4(1) := 1.U

}

...

}

when语句

通常用于给带使能信号的寄存器更新数据,对于有复位信号的寄存器推荐使用

RegInit声明,而非在when中使用Reset.asBool作为复位条件1

2

3

4

5when (condition 1) { definition 1 }

.elsewhen (condition 2) { definition 2 }

...

.elsewhen (condition N) { definition N }

.otherwise { default behavior }所有的

condition为Bool类型参数(非scala的Boolean),对于UInt、SInt、Reset类型可以使用asBool进行转换;建议将.otherwise写全,以防驱动不全。

第四章 Chisel常见硬件原语

Chisel语言库中定义了很多常用的硬件原语,可直接导入包来使用,进而搭建大型电路

多路选择器

二路选择器

Mux(sel,in1,in2)(chisel3)嵌套使用:

Mux(c1,a,Mux(c2,b,Mux(...,default)))MuxCase(default,Array(c1->a,c2->b,...))(chisel3.util)——(成立的条件 -> 被选择的输入)MuxLookup(idx,default,Array(0.U->a,1.U->b,...))(chisel3.util)——成立条件为从0开始的索引,相当于MuxCase(default,Array((idx===0.U)->a,(idx===1.U)->b,...))Mux1H(chisel3.util)——选择信号为独热码PriorityMux(chisel3.util)——多个选择信号有效按优先级(靠前的优先)选择

注:在Verilog中使用always编写能综合出时序逻辑和组合逻辑,导致reg变量存在二义性;if…else语句不能传播位置态x,导致仿真阶段不能发现一些问题,故工业级Verilog代码大多用assign构建电路。

优先编码器

对多个输入信号中优先级最高的信号进行编码

PriorityEncoder——返回UIntPriorityEncoderOH——编码结果转换成独热码,返回UInt或Seq

仲裁器

Arbiter优先仲裁器(chisel3.util中,指定义了类,没有单例对象,每次要通过new来创建)使用标准

ready-valid接口,其内部使用ArbiterIO调用Decoupled单例对象来创建端口;ready-valid接口信号:(1)ready—consumer准备好接收;(2)valid—producer准备好发送;(3)bits—传输的数据对于

Decoupled创建的端口直接使用<>进行连接,体现了接口的意义其内部包含和n个

poducter连接,一个和consumer连接的ready-valid接口,以及一个表示最终选择结果(从0开始的索引)的chosen变量:1

2

3

4

5class ArbiterIO[T <: Data](private val gen: T, val n: Int) extends Bundle {

val in = Flipped(Vec(n, Decoupled(gen)))

val out = Decoupled(gen)

val chosen = Output(UInt(log2Ceil(n).W))

}定义仲裁器并例化——生成的Verilog代码会生成两个模块,一个是例化的

Arbiter,一个是其顶层模块MyArbiter1

2

3

4

5

6

7

8

9

10

11

12

13

14import chisel3._

import chisel3.util._

class MyArbiter extends Module {

val io = IO(new Bundle {

val in = Flipped(Vec(2, Decoupled(UInt(8.W))))

val out = Decoupled(UInt(8.W))

val chosen = Output(UInt())

})

val arbiter = Module(new Arbiter(UInt(8.W), 2)) // 2 to 1 Priority Arbiter

arbiter.io.in <> io.in

io.out <> arbiter.io.out

io.chosen := arbiter.io.chosen

}

RRArbiter循环仲裁器——使用同Arbiter,仅内部实现不同

队列

Queue类及其单例对象(chisel3.util)——创建一个使用ready-valid接口的FIFO;内部使用

QueueIO定义端口,同样调用Decoupled:1

2

3

4

5

6

7

8

9

10

11

12class QueueIO[T <: Data](private val gen: T, val entries: Int) extends Bundle

{

val enq = Flipped(EnqIO(gen)) //write data 与producer连接

val deq = Flipped(DeqIO(gen)) //read data 与consumer连接

val count = Output(UInt(log2Ceil(entries + 1).W)) //数据个数

}

object EnqIO {

def apply[T<:Data](gen: T): DecoupledIO[T] = Decoupled(gen)

}

object DeqIO {

def apply[T<:Data](gen: T): DecoupledIO[T] = Flipped(Decoupled(gen))

}因定义了

Queue类及其单例对象,故有两种使用方式,一种与Arbiter相同,使用new Queue(gen:T,entries:Int)1

2

3

4

5

6

7

8

9

10

11class MyQueue extends Module {

val io = IO(new Bundle {

val in = Flipped(Decoupled(UInt(8.W)))

val out = Decoupled(UInt(8.W))

val cnt = Output(UInt(4.W))

})

val q = Module(new Queue(UInt(8.W), entries = 16))

q.io.enq <> io.in

io.out <> q.io.deq

io.cnt := q.io.count

}另一种使用

Queue(enq:ReadyValidIO[T],entries:Int=2)第一个参数直接传入enq,该方式返回deq,因此不能在代码中直接访问enq和count【不会生成io_count,但可通过io.deq.valid和io.enq.ready简介访问empty和full信号】

1

2

3

4

5

6

7

8class MyQueue extends Module {

val io = IO(new Bundle {

val in = Flipped(Decoupled(UInt(8.W)))

val out = Decoupled(UInt(8.W))

})

val q = Queue(io.in, 2)

io.out <> q

}

ROM

可通过工厂方法

VecInit[T<:Data](elt0:T,elts:T*)或VecInit[T<:Data](elts:Seq[T])创建1

2

3

4

5

6

7

8

9class Rom extends Module {

val io = IO(new Bundle {

val sel = Input(UInt(3.W))

val out = Output(UInt(8.W))

})

val rom = VecInit(10.U, 20.U, 30.U, 40.U, 50.U, 60.U, 70.U, 80.U))

io.out := rom(io.sel)

}RAM

使用工厂方法

Mem[T<:Data](size:Int,t:T)构建同步写,异步读RAM(会被综合成寄存器序列)1

val asyncMem = Mem(16, UInt(32.W))

使用

SyncReadMem[T<:Data](size:Int,t:T)构建同步读写RAM(被综合成SRAM,使能信号都可省略)若读写互斥,RAM会被推断为单端口RAM

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20class SinglePortRAM extends Module {

val io = IO(new Bundle {

val addr = Input(UInt(10.W))

val dataIn = Input(UInt(32.W))

val en = Input(Bool())

val we = Input(Bool())

val dataOut = Output(UInt(32.W))

})

val syncRAM = SyncReadMem(1024, UInt(32.W))

when(io.en) {

when(io.we.asBool()) {

syncRAM.write(io.addr, io.dataIn)

io.dataOut := DontCare

}.otherwise {

io.dataOut := syncRAM.read(io.addr)

}

}.otherwise {

io.dataOut := DontCare

}

}也可以不使用

write和read方法,直接使用赋值语句:1

2

3

4

5

6

7

8

9

10

11val mem = SyncReadMem(1024, UInt(width.W))

io.dataOut := DontCare //若不写,需在when的otherwise中补全DontCare驱动

when(io.enable) {

val rdwrPort = mem(io.addr)

when(io.write) {

rdwrPort := io.dataIn

}

.otherwise {

io.dataOut := rdwrPort

}

}反之为双端口RAM

1

2

3

4val mem = SyncReadMem(1024, UInt(width.W))

// Create one write port and one read port

mem.write(io.addr, io.dataIn)

io.dataOut := mem.read(io.addr2, io.enable)

带写掩码的RAM

当构建RAM的数据类型为

Vec[T]时,就会推断出有写掩码,需要定义一个Seq[Bool]的掩码信号,序列元素的个数为写入端口位宽除以字节宽度(故需按字节写入),使用write的重载版本1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28import chisel3._

import chisel3.util._

class MaskRAM extends Module {

val io = IO(new Bundle {

val addr = Input(UInt(10.W))

val dataIn = Input(UInt(32.W))

val en = Input(Bool())

val we = Input(Bool())

val mask = Input(Vec(4, Bool()))

val dataOut = Output(UInt(32.W))

})

val dataIn_temp = Wire(Vec(4, UInt(8.W)))

val dataOut_temp = Wire(Vec(4, UInt(8.W)))

val syncRAM = SyncReadMem(1024, Vec(4, UInt(8.W)))

dataOut_temp := DontCare

when(io.en) {

when(io.we) {

syncRAM.write(io.addr, dataIn_temp, io.mask)

}.otherwise {

dataOut_temp := syncRAM.read(io.addr)

}

}

for (i <- 0 until 4) {

dataIn_temp(i) := io.dataIn(8 * i + 7, 8 * i)

io.dataOut := Cat(dataOut_temp(3), dataOut_temp(2), dataOut_temp(1), dataOut_temp(0))

}

}从文件读取数据到RAM

使用

experimental包的单例对象loadMemoryFromFile的apply方法:、def apply[T <: Data](memory: MemBase[T], fileName: String, hexOrBinary: FileType = MemoryLoadFileType.Hex): Unit实际就是调用Verilog的系统函数

$readmemh和$readmemb第一个参数是

MemBase[T]类型的,也就是Mem[T]和SyncReadMem[T]的超类,该参数接收一个自定义的RAM对象;第二个参数是文件的名字及路径,用字符串表示;第三个参数表示读取的方式为十六进制或二进制,默认是MemoryLoadFileType.Hex,也可以改成MemoryLoadFileType.Binary。注意,没有十进制和八进制。1

2

3

4

5

6

7

8

9

10

11

12

13import chisel3._

import chisel3.util.experimental.{loadMemoryFromFile,loadMemoryFromFileInline}

class LoadMem extends Module {

val io = IO(new Bundle {

val address = Input(UInt(3.W))

val value = Output(UInt(8.W))

})

val memory = Mem(8, UInt(8.W))

io.value := memory.read(io.address)

loadMemoryFromFile(memory, "/chisel-examples/mem.txt")

}

//将生成两个文件,LoadMem和BindsTo_0_LoadMem两个模块loadMemoryFromFileInLine(chisel3.4.3)使用方法与1.相同,但将读取文件数据代码直接嵌入LoadMem模块中。使用RAM实现一个带有空、满标志的8bit同步FIFO模块

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36class SynFifo extends Module{

val io = IO(new Bundle() {

val enq = Flipped(Decoupled(UInt(32.W)))

val deq = Decoupled(UInt(32.W))

val full = Output(Bool())

val empty = Output(Bool())

})

val addrwidth = 8

val datawidth = 32

val addrin = RegInit(0.U((addrwidth + 1).W))

val addrout = RegInit(0.U((addrwidth + 1).W))

val mem = SyncReadMem(256, UInt(datawidth.W))

when((io.enq.valid === 1.B) && (io.enq.ready === 1.B)){

mem.write(addrin, io.enq.bits)

addrin := addrin + 1.U

}

when((io.deq.valid === 1.B) && (io.deq.ready === 1.B)){

io.deq.bits := mem.read(addrout)

}.otherwise{

io.deq.bits := DontCare

}

io.empty := ~io.deq.valid

io.full := ~io.enq.ready

when(addrout(addrwidth - 1,0) === addrin(addrwidth - 1,0)){

when(addrout(addrwidth) === addrin(addrwidth)){

io.deq.valid := 0.B

io.enq.ready := 1.B

}.otherwise{

io.deq.valid := 1.B

io.enq.ready := 0.B

}

}.otherwise{

io.deq.valid := 1.B

io.enq.ready := 1.B

}

}

计数器Counter

三种实现方式及从0计数到233的三种版本:

def apply(cond:Bool,n:Int):(UInt,Bool)第一个参数是Bool类型的使能信号,为true.B时计数器从0开始每个时钟上升沿加1自增,为false.B时则计数器保持不变;第二个参数需要一个Int类型的具体正数,当计数到n时归零。 该方法返回一个二元组:其第一个元素是计数器的计数值,第二个元素是判断计数值是否等于n的结果

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15import chisel3._

import chisel3.util._

class MyCounter extends Module {

val io = IO(new Bundle {

val en = Input(Bool())

val out = Output(UInt(8.W))

val valid = Output(Bool())

})

val (a, b) = Counter(io.en, 233)

io.out := a

io.valid := b

}def apply(r:Range,enable:Bool=true.B,reset:Bool=false.B):(UInt,Bool)1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16import chisel3._

import chisel3.util._

import scala.collection.immutable.Range

class MyCounter extends Module {

val io = IO(new Bundle {

val en = Input(Bool())

val out = Output(UInt(8.W))

val valid = Output(Bool())

})

val (a, b) = Counter(Range(0,233),io.en)

io.out := a

io.valid := b

}def apply(n: Int): Counter1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20import chisel3._

import chisel3.util._

class MyCounter extends Module {

val io = IO(new Bundle {

val en = Input(Bool())

val out = Output(UInt(8.W))

val valid = Output(Bool())

})

val cnt = Counter(233)

when(io.en){

cnt.inc()

}

val a = cnt.value

val b = cnt.value === cnt.n.U

io.out := a

io.valid := b

}使用Counter搭建四分频电路:

1

2

3

4

5

6

7

8class FourFreDiv extends Module{

val io = IO(new Bundle {

val en = Input(Bool())

val clk_4 = Output(Bool())

})

val (a, b) = Counter(io.en, 4)

io.clk_4 := a(1)

}

线性反馈移位寄存器

LFSR(chisel3.util.random)

def apply(width: Int, increment: Bool = true.B, seed: Option[BigInt] = Some(1)): UInt:产生伪随机数- 第一个参数是寄存器的位宽。

- 第二个参数是一个

Bool类型的使能信号,用于控制寄存器是否移位,缺省值为true.B。 - 第三个参数是一个随机种子,是可选值类型。

1

2

3

4

5

6

7

8

9

10import chisel3._

import chisel3.util._

class LFSR16 extends Module {

val io = IO(new Bundle {

val en = Input(Bool())

val out = Output(UInt(16.W))

})

io.out := LFSR(16,io.en,Some(1))

}状态机

使用util包中的

Enum特质及其伴生对象def apply(n:Int):List[UInt],与枚举的状态名对应起来,在switch...is...is语句中使用【注:枚举状态名首字母需小写才能被scala编译器识别为变量模式匹配】例如检测时间超过两个时钟周期的高电平:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33import chisel3._

import chisel3.util._

class DetectTwoOnes extends Module {

val io = IO(new Bundle {

val in = Input(Bool())

val out = Output(Bool())

})

val sNone :: sOne1 :: sTwo1s :: Nil = Enum(3)

val state = RegInit(sNone)

io.out := (state === sTwo1s)

switch(state) {

is(sNone) {

when(io.in) {

state := sOne1

}

}

is(sOne1) {

when(io.in) {

state := sTwo1s

}.otherwise {

state := sNone

}

}

is(sTwo1s) {

when(!io.in) {

state := sNone

}

}

}

}

[2]CPU制作入门[^5]

第一、二章 计算机架构

- 基本逻辑and、or、not的电路实现(二极管)->实现所有门电路->SR触发器的实现【数电】

- 组合逻辑:时钟沿更新状态->使用组合逻辑输入输出,D锁存器、D触发器(两个D锁存器构成,只在上升沿将状态传递给从锁存器,阻隔状态不稳定的跳变)【数电】

- 计算机架构:输入输出、存储、数据控制通路;计算机基本处理流程:取指、译码、运算、访存、写回;译码通过特征值(funct7、funct3、opcode)来判断指令类型,而且指令定长和操作数位置对齐方便译码;

第三章 Chisel基础

变量

var(可重新赋值)和val(不可~,硬件);def——定义对象具有的行为;Seq——有序集合,从0开始索引;class——对象,可继承;object——单例对象,有实例的类(常用作含工厂方法【生成实例的方法,apply()方法】的伴生对象),如下:1

2

3

4

5

6

7

8

9

10

11

12

13//含工厂方法的伴生对象示例

class Example(a:Int){

val hoge=a

}

object Example{

def apply(a:Int)={

new Example(a)

}

}

//apply()方法的生成实例

val x=Example.apply(1)

//在scala中apply()方法可省略其描述

val y=Example(2)命名空间——文件开头的

package 名指定文件所属命名空间,通过命名空间引用里面的类eg:val a=new package_name.class_name;import——可省略命名空间直接引用控制电路:BitPat对象——用作条件表达式,eg:

"b10101".U===BitPat("101??")//true.B,其中?表无关位;用BitPat定义指令位列,eg:val ADD=BitPat("???0100???")位操作:

Cat对象——连接位列,eg:Cat("b101".U,"b11".U)//"b10111.U"或Cat(Seq("b101".U,"b11".U))//"b10111.U";Fill对象——重复位列,eg:Fill(3,1.U)//111.U打印参数:

printf——变量前加$,字符串前加p,嵌入表达式时用{}括起来,eg:printf(p”hex:0x${Hexadecimal(inst)}\n”)`

第四章 环境架构

项目源码chisel-temple下载: 简单RISC-V CPU——chisel-temple (实现I、部分V、Zicsr指令)【包含定义指令、常量文件,系统代码】

docker环境搭建

windows: Windows | Docker Docs

安装下载后命令行输入

docker version显示版本号即下载成功打开Docker Desktop即开启docker服务,若显示“docker engine stopped”则右键“docker restart”

ubuntu: 在 Ubuntu 上安装与配置 Docker )

第五章 取指令的实现

常量定义

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18package public

import chisel3._

object Consts {

//Memory

val WORD_LEN = 32

//Instruction Memory

val IMEM_WIDTH = 32 //32bit

val IMEM_DEPTH = 16384 //16KB

val IMEM_HEX_PATH = "src/main/resources/test.hex"

//Rigister

val RegNum = 32

val START_ADDR = 0.U(WORD_LEN.W) //PC start address

}指令存储器模块

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40package cpu

import chisel3._

import chisel3.util._

import chisel3.util.experimental.loadMemoryFromFile

import public.Consts._

/*

type: IO Port

name: InstMemPortIO(指令存储器接口)

addr: Memory address,input

inst: Instruction,output

*/

class InstMemPortIO extends Bundle {

val addr = Input(UInt(WORD_LEN.W))

val inst = Output(UInt(WORD_LEN.W))

}

/*

type: Hardware

name: InstMem(指令存储器)

*/

class InstMem extends Module {

val io = IO(new Bundle {

val instmem = new InstMemPortIO()

})

//Instruction Memory Size: 16KB(16384 * 8bits)

val mem = Mem(IMEM_DEPTH, UInt(8.W))

loadMemoryFromFile(mem, IMEM_HEX_PATH)

//connect the 4 address to get a 32-bit instruction

io.instmem.inst := Cat(

mem(io.instmem.addr + 3.U(WORD_LEN.W)),

mem(io.instmem.addr + 2.U(WORD_LEN.W)),

mem(io.instmem.addr + 1.U(WORD_LEN.W)),

mem(io.instmem.addr)

)

}cpu模块

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34package cpu

import chisel3._

import chisel3.util._

import public.Consts._

class Core extends Module{

val io = IO(new Bundle{

val instmem = Flipped(new InstMemPortIO())

// val gp = Output(UInt(WORD_LEN.W))

val exit = Output(Bool()) //turn to true.B when pc reach the end of the instruction memory(inst:0x34333231)

})

//32x32bit general purpose register and a 32-bit program counter

val reg_x = Mem(RegNum, UInt(WORD_LEN.W))

val reg_pc = RegInit(START_ADDR)

//**************************************

//Instruction Fetch (IF) Stage

reg_pc := reg_pc + 4.U(WORD_LEN.W) //pc+4 in each clock cycle

io.instmem.addr := reg_pc

val inst = io.instmem.inst

io.exit := (inst === 0x34333231.U(WORD_LEN.W))

//**************************************

//print

printf(p"reg_pc: 0x${Hexadecimal(reg_pc)}\n")

printf(p"inst: 0x${Hexadecimal(inst)}\n")

printf("-----------------------------\n")

}顶层模块

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16package cpu

import chisel3._

import chisel3.util._

class Top extends Module{

val io = IO(new Bundle{

val exit = Output(Bool())

})

val core = Module(new Core)

val instmem = Module(new InstMem)

core.io.instmem <> instmem.io.instmem

io.exit := core.io.exit

}

第六章 用ChiselTest进行取指令测试

sbt(scala build tool)的build.sbt指定读取库,在

libraryDependencies中增加organization %% moduleName % version % configuration1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23// See README.md for license details.

ThisBuild / scalaVersion := "2.12.12"

ThisBuild / version := "0.1.0"

ThisBuild / organization := "%ORGANIZATION%"

lazy val root = (project in file("."))

.settings(

name := "%NAME%",

libraryDependencies ++= Seq(

"edu.berkeley.cs" %% "chisel3" % "3.4.2",

"edu.berkeley.cs" %% "chiseltest" % "0.3.2" % "test"

),

scalacOptions ++= Seq(

"-Xsource:2.11",

"-language:reflectiveCalls",

"-deprecation",

"-feature",

"-Xcheckinit"

),

addCompilerPlugin("edu.berkeley.cs" % "chisel3-plugin" % "3.4.2" cross CrossVersion.full),

addCompilerPlugin("org.scalamacros" % "paradise" % "2.1.1" cross CrossVersion.full)

)创建Chisel测试代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15package cpu

import chisel3._

import org.scalatest._

import chiseltest._

class CPUTest extends FlatSpec with ChiselScalatestTester {

"mycpu" should "work through hex" in {

test(new Top) { c =>

while (!c.io.exit.peek().litToBoolean){

c.clock.step(1)

}

}

}

}测试类

class Test继承两个trait(特征):FlatSpec和ChiselScalatestTesterFlatSpec是scala测试框架ScalaTest(package org.scalatest内定义的trait,为每个测试提供文本标记测试对象行为的should()方法:1

2

3"测试目标名" should "正确行为" in{

//测试内容

}ChiselScalatestTester是package chiseltest中定义的trait,提供测试chisel中定义的硬件模块test()方法peek()方法——用信号名.peek()获取值clock.step()方法——[实例].clock.step(n)将时钟提前n个循环在测试对象类里添加

printf打印运行时信息运算测试

sbt "testOnly package名.测试类",测试结果:1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27[info] welcome to sbt 1.9.7 (Oracle Corporation Java 1.8.0_301)

[info] loading settings for project chisel-chip-build from plugins.sbt ...

[info] loading project definition from C:\Users\SWQ2003\Desktop\CPU-code\Chisel-Chip\project

[info] loading settings for project root from build.sbt ...

[info] set current project to %NAME% (in build file:/C:/Users/SWQ2003/Desktop/CPU-code/Chisel-Chip/)

[info] compiling 1 Scala source to C:\Users\SWQ2003\Desktop\CPU-code\Chisel-Chip\target\scala-2.12\classes ...

Elaborating design...

Done elaborating.

reg_pc: 0x00000000

inst: 0x14131211

-----------------------------

reg_pc: 0x00000004

inst: 0x24232221

-----------------------------

reg_pc: 0x00000008

inst: 0x34333231

-----------------------------

test Top Success: 0 tests passed in 4 cycles in 0.040025 seconds 99.94 Hz

[info] CPUTest:

[info] mycpu

[info] - should work through hex

[info] Run completed in 2 seconds, 191 milliseconds.

[info] Total number of tests run: 1

[info] Suites: completed 1, aborted 0

[info] Tests: succeeded 1, failed 0, canceled 0, ignored 0, pending 0

[info] All tests passed.

[success] Total time: 7 s, completed 2025-2-23 18:40:22

第七章 指令译码器的实现

从指令中提取rs1、rs2、rd,在core类中添加如下代码

1 | //Instruction Decode (ID) Stage |

其中地址的获取直接通过UInt的apply方法获取从高位到低位的子集;数据的获取通过二路选择器Mux,在地址为0时固定输出0(x0寄存器固定全0)

第八章 LW指令的实现

lw rd,offset(rs1)——从存储器中读取1字(1word)数据

x[rd]=M[x[rs1]+sext(imm_i)]【sext()表符号拓展,用imm_i的最高位进行】

| name | type | 31~20 | 19~15 | 14~12 | 11~7 | 6~0 |

|---|---|---|---|---|---|---|

| LW | “I”格式 | imm_i[11:0] | rs1 | 010 | rd | 0000011 |

增加对LW指令的定义

1

2

3

4

5

6

7package public

import chisel3.util._

object Instructions{

val LW = BitPat("b?????????????????010?????0000011")

}修改存储器,增加接口和读取逻辑

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18/*

type: IO Port

name: DataMemPortIO(数据存储器接口)

addr: Memory address,input

data: Data,output

*/

class DataMemPortIO extends Bundle {

val addr = Input(UInt(WORD_LEN.W))

val data = Output(UInt(WORD_LEN.W))

}

io.datamem.data := Cat(

mem(io.datamem.addr + 3.U(WORD_LEN.W)),

mem(io.datamem.addr + 2.U(WORD_LEN.W)),

mem(io.datamem.addr + 1.U(WORD_LEN.W)),

mem(io.datamem.addr)

)top顶层模块连接新建接口

1

core.io.datamem <> instmem.io.datamem

core类中增加立即数imm_i(i型指令的立即数)的提取及位拓展

1

2val imm_i = inst(31, 20) //I-type imm

val imm_i_sext = Cat(Fill(20, imm_i(11)), imm_i) //sign-extend imm_i增加执行、访存和写回

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17//Instruction Execute (EX) Stage

val alu_out = MuxCase(0.U(WORD_LEN.W), Seq(

(inst === LW) -> (rs1_data + imm_i_sext),

))

//Memory Access (MEM) Stage

when(inst === LW){

io.datamem.addr := alu_out

}.otherwise{

io.datamem.addr := 0.U(WORD_LEN.W)

}

//Write Back (WB) Stage

val rd_data = io.datamem.data

when(inst === LW){

reg_x(rd_addr) := rd_data

}这里如果不加.otherwise会报错

io.datamem.addr驱动不全,也可以省略when()语句,直接赋值io.datamem.addr := alu_out因alu_out有默认值。

第九章 SW指令的实现

sw rs2,offset(rs1)——向存储器中存入1字(1word)数据

M[x[rs1]+sext(imm_s)]=x[rs2]【sext()表符号拓展,用imm_i的最高位进行】

| name | type | 31~25 | 24~20 | 19~15 | 14~12 | 11~7 | 6~0 |

|---|---|---|---|---|---|---|---|

| SW | “S”格式 | imm_s[11:5] | rs2 | rs1 | 010 | imm_s[4:0] | 0100011 |

第十、十一章 加减法和逻辑运算指令的实现

add rd,rs1,rs2;sub rd,rs1,rs2——R型指令

addi rd,rs1,imm_i——I型指令

| name | type | 31~25 | 24~20 | 19~15 | 14~12 | 11~7 | 6~0 |

|---|---|---|---|---|---|---|---|

| ADD | “R”格式 | 0000000 | rs2 | rs1 | 000 | rd | 0110011 |

| SUB | “R”格式 | 0100000 | rs2 | rs1 | 000 | rd | 0110011 |

在EX阶段添加alu_out相应运算代码,在WB阶段增加写回寄存器

1 | //Instruction Execute (EX) Stage |

逻辑运算同理

1 | and rd,rs1,rs2; andi rd,rs1,imm_i |

第十二章 译码器的强化

主要将每个阶段的操作或值的选取方式分类,然后在译码阶对应到相应操作和值的选取方式上,免去了大量操作的重写。

【分类:ALU_或BR_操作、OP1_(操作数1选择)、OP2_(操作数2选择)、MEM_(存储器写使能)、WB_(写回值选择)、REN_(写回使能)、CSR_(CSR值选择)】

1 | //首先将rd、rs1、rs2、imm_i等从指令中提取出来备用,不管该指令是何种类型 |

第十三、十四章 移位和比较运算的实现

移位和比较指令都为R和I格式指令

1 | sll rd,rs1,rs2; slli rd,rs1,shamt//逻辑左移 |

比较运算若第一操作数小于第二操作数,则向x[rd]写入1(slt:set if less than)

1 | slt rd,rs1,rs2; slti rd,rs1,imm_i//有符号数 |

首先在指令定义中加入定义,然后在ID阶段将操作和操作数对应,在EX阶段ALU执行相应运算操作(chisel的比较运算符返回Bool类型,需用asUInt()方法转换为UInt类型)

1 | (exe_fun === ALU_SLL) -> (op1_data << op2_data(4, 0))(31, 0), |

第十五、十六章 分支和跳转指令的实现

分支指令都为B格式指令,未指定imm[0]的值(始终为0,因跳转地址至少是2的倍数【最短的16位压缩扩展指令C为2字节】),故可扩大跳转范围,用12为地址跳转到13位的范围

1

2

3

4

5

6beq rs1,rs2,offset

bne rs1,rs2,offset

blt rs1,rs2,offset//x[rs1] <s x[rs2]

bge rs1,rs2,offset//x[rs1] >=s x[rs2]

bltu rs1,rs2,offset//x[rs1] <u x[rs2]

bgeu rs1,rs2,offset//x[rs1] >=u x[rs2]需要定义变量br_flag和br_target,br_flag的计算需添加类似alu_out的逻辑,br_target在br_flag为真时赋给reg_pc_next

jalr(jump and link register)为I格式;jal为j格式,最低位和b格式一样始终为0。

1

2jal rd,offset

jalr rd,offset(rs1)x[rd]寄存器写回PC+4(通常为x[1]的ra寄存器【return address】);下一个循环PC分别为

PC+sext(imm_j)和(x[rs1]+sext(imm_i))&~1(与~1将最低位清零【来自x[rs1]】)增加j格式指令立即数译码逻辑;op1增加取pc值逻辑;op2增加取imm_j逻辑;alu_out增加jalr的运算;增加pc值更新逻辑(为在IF阶段使用alu_out,需提前用wire对象声明【线路回连】);在写回阶段增加PC值+4的写回

1

2

3

4

5

6

7

8//program counter update

val reg_pc_next_default = reg_pc + 4.U(WORD_LEN.W)

val reg_pc_next = MuxCase(reg_pc_next_default, Seq(

br_flag -> br_target,

jmp_flag -> alu_out,

(inst === ECALL) -> reg_csr(0x305) // go to trap_vector

))

reg_pc := reg_pc_next1

2

3

4

5

6

7

8

9

10

11

12

13val op1_data = MuxCase(0.U(WORD_LEN.W), Seq(

(op1_sel === OP1_RS1) -> rs1_data,

(op1_sel === OP1_PC ) -> reg_pc,

(op1_sel === OP1_IMZ) -> imm_z_uext

))

val op2_data = MuxCase(0.U(WORD_LEN.W), Seq(

(op2_sel === OP2_RS2) -> rs2_data,

(op2_sel === OP2_IMI) -> imm_i_sext,

(op2_sel === OP2_IMS) -> imm_s_sext,

(op2_sel === OP2_IMJ) -> imm_j_sext,

(op2_sel === OP2_IMU) -> imm_u_shifted

))1

2

3

4

5

6

7

8

9

10//branch

br_target := reg_pc + imm_b_sext

br_flag := MuxCase(false.B, Seq(

(exe_fun === BR_BEQ) -> (op1_data === op2_data),

(exe_fun === BR_BNE) -> !(op1_data === op2_data),

(exe_fun === BR_BLT) -> (op1_data.asSInt() < op2_data.asSInt()),

(exe_fun === BR_BGE) -> !(op1_data.asSInt() < op2_data.asSInt()),

(exe_fun === BR_BLTU) -> (op1_data < op2_data),

(exe_fun === BR_BGEU) -> !(op1_data < op2_data)

))1

2

3

4

5val rd_data = MuxCase(alu_out, Seq(

(rd_sel === WB_MEM) -> io.datamem.rdata,

(rd_sel === WB_PC) -> reg_pc_next_default,

(rd_sel === WB_CSR) -> csr_rdata

))

第十七章 立即数加载指令的实现

1 | lui rd,imm_u //将sext(imm_u[31:12]<<12)写入x[rd],U格式 |

因立即数偏移12位,而jalr的imm_i是12位的,故组合可跳转32位范围内任意地址;

同样AUIPC和LW或SW组合可访问32位存储器;

使用addi rd,x0,imm可获得立即数低12位,和LUI或AUIPC的高20位组成32位立即数

第十八、十九章 CSR指令和ECALL的实现

CSR寄存器:12位地址,存储状态与控制信息,示例:

| 地址 | 名称 | 记忆的数据 |

|---|---|---|

| 0x300 | mstatus | 机器状态(中断许可等) |

| 0x305 | mtvec | 异常模式下发生异常时的处理陷阱向量地址 |

| 0x341 | mepc | 机器模式下发生异常时的PC |

| 0x342 | mcause | 机器模式下发生中断/异常时的主要原因 |

I格式指令,原2031位imm_i变为CSR地址;1519位变为rs1和imm_z(CSR指令用5位立即数)复用

1 | csrrw rd,csr,rs1; csrrwi rd,csr,imm_z //read & write |

| 指令 | 至CSRs[csr]的写入数据 | 至x[rd]的写入数据 |

|---|---|---|

| CSRRW | x[rs1] | CSRs[csr] |

| CSRRW | uext(imm_z) | CSRs[csr] |

| CSRRW | CSRs[csr] | x[rs1] | CSRs[csr] |

| CSRRW | CSRs[csr] | uext(imm_z) | CSRs[csr] |

| CSRRW | CSRs[csr] & ~ x[rs1] | CSRs[csr] |

| CSRRW | CSRs[csr] & ~ uext(imm_z) | CSRs[csr] |

uext(imm_z)将5位以上用0位拓展;先读后写入更新值

对CORE代码的更新首先在ID阶段,加入对CSR操作的分类项val exe_fun :: op1_sel :: op2_sel :: mem_wen :: rd_wen :: rd_sel :: csr_cmd :: Nil = inst_type【因CSR亦涉及到op1、op2、WB阶段的分类,尽管为了几条CSR指令新建一个新译码类,但整体上还是有必要的】;加入CSR读取、运算、写入代码***【MEM阶段,最佳位置仍待商讨】***,加入WB阶段选择代码

ecall指令的7~31皆为0,执行ecall首先将模式值写入CSR的mcause寄存器(0x342),机器模式为11;然后跳转到CSR的mtvec中保存的trap_vector地址(其描述了异常发生时的处理(系统调用)【在无运行环境的Chisel实现中,跳转到trap_vector会触发riscv-tests结束】);最后将异常发生时的PC写入mepc,将各种状态写入mstatus

因只涉及到CSR操作,只需在ID导入后,在PC、MEM添加相关代码即可。

第二十、二十一章 用riscv-tests和C程序进行测试(在linux平台进行)

riscv-tests 是RISC-V生态中的开源测试包,可以自动针对不同指令进行动作确认和CPU性能测量

若无法搭建riscv-gnu环境,可在项目源码目录riscv-chisel-book-master\target\share\riscv-tests\isa中找到相应指令的.dump文件,但仍需编译成二进制文件

安装 riscv-gnu-toolchain: GNU toolchain for RISC-V [^15]

官方源:

1

2

3git clone https://github.com/riscv/riscv-gnu-toolchain

sudo apt-get install autoconf automake autotools-dev curl python3 python3-pip python3-tomli libmpc-dev libmpfr-dev libgmp-dev gawk build-essential bison flex texinfo gperf libtool patchutils bc zlib1g-dev libexpat-dev ninja-build git cmake libglib2.0-dev libslirp-dev

git submodule update --init --recursive国内镜像:(参考: riscv-gnu-toolchain工具链和模拟器安装记录 ; riscv-gnu-toolchain工具链 )

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37# 从gitee国内镜像下载速度很快

git clone https://gitee.com/mirrors/riscv-gnu-toolchain.git

cd riscv-gnu-toolchain

git clone https://gitee.com/mirrors/riscv-dejagnu

git clone -b riscv-gcc-10.2.0 https://gitee.com/mirrors/riscv-gcc

git clone -b riscv-glibc-2.29 https://gitee.com/mirrors/riscv-glibc

git clone https://gitee.com/mirrors/riscv-newlib

git clone -b riscv-binutils-2.35 https://gitee.com/mirrors/riscv-binutils-gdb riscv-binutils

git clone -b fsf-gdb-10.1-with-sim https://gitee.com/mirrors/riscv-binutils-gdb riscv-gdb

# 将下载的库改名(去掉riscv-)

# 安装相应依赖库

sudo apt-get install autoconf automake autotools-dev curl python3 libmpc-dev libmpfr-dev libgmp-dev gawk build-essential bison flex texinfo gperf libtool patchutils bc zlib1g-dev libexpat-dev ninja-build

# 创建riscv文件夹,并设置权限

sudo mkdir /opt/riscv

sudo chmod 777 /opt/riscv

# 编辑.bashrc文件

sudo vim ~/.bashrc

# 在.bashrc文件末尾添加这两句

export RISCV=/opt/riscv

export PATH=$RISCV/bin:$PATH

# 让环境变量生效

source ~/.bashrc

# 如果只构建32位的交叉编译器,执行

./configure --prefix=/opt/riscv --with-arch=rv32gc --with-abi=ilp32d

# 构建64位的交叉编译器,执行

./configure --prefix=/opt/riscv

# 构建同时支持32位和64位的交叉编译器,执行 (推荐!)

./configure --prefix=/opt/riscv --enable-multilib

# Newlib执行,编译elf-gcc版本。使用的是riscv-newlib库(面向嵌入式的C库),只支持静态链接,不支持动态链接。

sudo make -j `nproc`

# linux执行这个,编译linux-gnu-gcc版本。使用的是glibc标准库,支持动态链接。

sudo make linux -j `nproc`安装 riscv-software-src/riscv-tests

1

2

3

4git clone https://github.com/riscv-software-src/riscv-tests.git

cd riscv-tests

git submodule update --init --recursive

cd /env/p/link.ld支持测试的代码前缀:

TVM Name Description rv32uiRV32 user-level, integer only rv32siRV32 supervisor-level, integer only rv64uiRV64 user-level, integer only rv64ufRV64 user-level, integer and floating-point rv64uvRV64 user-level, integer, floating-point, and vector rv64siRV64 supervisor-level, integer only rv64svRV64 supervisor-level, integer and vector Target Environment Name Description pvirtual memory is disabled, only core 0 boots up pmvirtual memory is disabled, all cores boot up ptvirtual memory is disabled, timer interrupt fires every 100 cycles vvirtual memory is enabled - 、将起始地址从0x80000000改为0x00000000

1

2

3

4SECTIONS

{

. = 0x00000000;

...在riscv-tests目录下执行

1

2

3

4autoconf

./configure --prefix=/opt/riscv/target

make

make install注:如果在riscv-tests下直接make报错以下内容,是因为isa中部分用例版本库不配

/opt/riscv/lib/gcc/riscv64-unknown-elf/10.2.0/../../../../riscv64-unknown-elf/bin/ld: error: /opt/riscv/lib/gcc/riscv64-unknown-elf/10.2.0/rv32i/ilp32/crtbegin.o: Mis-matched ISA version for ‘i’ extension. 2.0 vs 2.1

可以进入isa目录编译需要使用的指令集,在isa目录生成对应文件:

1

2

3cd isa

make rv32ui

make rv32mi将ELF文件转换为BIN文件

riscv64-unknown-elf-objcopy[ELF文件名][输出文件名]riscv64-unknown-elf-objcopy /isa/rv32ui-p-add rv32ui-p-add.binbin文件的十六进制化(以add指令为例)

使用od指令将文件转化为8进制或16进制,-An隐藏各行左端显示的地址信息;-t指定格式,x1表示1字节16进制;-w指定每行数据宽度,1行1字节;-v禁用以*省略相同内容的连续行

od -An -tx1 -w1 -v rv32ui-p-add.bin >> rv32ui-p-add.hex参考测试文件(eg.rv32ui-p-add.dump)修改

在dump文件中测试以pc=0x44结束,故

io.exit := (inst === EXIT_INST) || (reg_pc === EXIT_PC),val EXIT_PC = 0x44.U(WORD_LEN.W),同时添加x[3]即global pointer输出,在CPUTest中检测gp,若为1则通过测试在linux中进行批量测试脚本(批量使用

riscv64-unknown-elf-objcopy)批量生成hex文件

bash tohex.sh:1

2

3

4

5

6

7

8

9

10

11

12

13

14

FILES=./src/riscv-tests/isa/rv32*i-p-*

SAVE_DIR=./src/riscv-tests/isa/hex

for f in $FILES

do

FILE_NAME="${f##*/}"

if [[ ! $f =~ "dump" ]]; then

riscv64-unknown-elf-objcopy -O binary $f $SAVE_DIR/$FILE_NAME.bin

od -An -tx1 -w1 -v $SAVE_DIR/$FILE_NAME.bin > $SAVE_DIR/$FILE_NAME.hex

rm -f $SAVE_DIR/$FILE_NAME.bin

fi

done批量进行sbt测试:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

# .\rsicv-tests.sh <package name> <directory name>

# Example: .\riscv-tests.sh riscv-tests riscv-tests

UI_INSTS=(sw lw add addi sub and andi or ori xor xori sll srl sra slli srli srai slt sltu slti sltiu beq bne blt bge bltu bgeu jal jalr lui auipc)

MI_INSTS=(csr scall)

WORK_DIR=./src

RESULT_DIR=$WORK_DIR/riscv-tests/results

mkdir -p $RESULT_DIR

rm $RESULT_DIR/*.txt

function loop_test(){

INSTS=${!1}

PACKAGE_NAME=$2 #package name

ISA=$3

DIRECTORY_NAME=$4 #directory name

#change package name to $PACKAGE_NAME in CPUTests.scala

sed -e "s/{package}/$PACKAGE_NAME/" $WORK_DIR/riscv-tests/RiscvTests_temp.scala > $WORK_DIR/test/scala/riscv-tests/RiscvTests.scala

for INST in ${INSTS[@]}

do

echo $INST

#change package name and HEX file name in Memory.scala

sed -e "s/{package}/$PACKAGE_NAME/" -e "s/{isa}/$ISA/" -e "s/{inst}/$INST/" $WORK_DIR/riscv-tests/Mem_temp.scala > $WORK_DIR/main/scala/riscv-tests/Mem.scala

sbt "testOnly $PACKAGE_NAME.RiscvTest" > $RESULT_DIR/$INST.txt

done

}

PACKAGE_NAME=$1

DIRECTORY_NAME=$2

loop_test UI_INSTS[@] $PACKAGE_NAME "ui" $DIRECTORY_NAME

loop_test MI_INSTS[@] $PACKAGE_NAME "mi" $DIRECTORY_NAME首先替换模版文件RiscvTests_temp和Mem_temp中的标记{package}等,然后执行sbt test命令。注意测试文件的类名固定为

RiscvTest,自定义包名需遵守规则,路径名没影响。

c程序编译

使用

riscv64-unknown-elf-gcc -march=rv32i -mabi=ilp32 -c -o -test.o test.c-match=<isa>指定ISA;-mabi=<ABI>指定IBA;-c编译但不链接;-o<file>指定输出文件名将之前修改的链接脚本

link.ld复制到终端执行路径,执行命令:riscv64-unknown-elf-ld -b elf32-littleriscv test.o -T link.ld -o test生成可执行文件

最后再转换为bin文件即可

1

2

3riscv64-unknown-elf-objcopy -O binary test test.bin

od -An -tx1 -w1 -v test.bin >> ./hex/test.hex

riscv64-unknown-elf-objdump -b elf32-littleriscv -D test > ./dump/test.elf.dmp

第二十七章 向量指令VSETVLI

传统INTEL、ARM向量指令(SIMD)寄存器长度VLEN固定,有128、256和512位,软件需提前计算一次可运算的元素数VL,以及标准元素长度SEW,全部需软件指定,体现在指令中(eg.操作码为EVMX.512.0F.W0 28)。

RISC-V向量指令的寄存器长度可变;VLEN由硬件决定是固定值,软件只需提供SEW,因硬件会自动计算VL=VLEN/SEW。软硬件松耦合。

实现的基本指令:

VESTVLI:向量CSR设定指令

VLE32.V和VLE64.V:向量加载指令

VADD.VV:向量之间的加法指令

VSE32.V和VSE64.V:向量存储指令

VESTVLI指令(新增了7个向量CSR)

地址 名称 含义 0xC20 VL vectort length:每次计算的元素数 0xC21 VTYPE vector data type register:含SEW在内的各种运算信息 汇编描述:vsetvli rd,rs1,vtypei

31~20 19~15 14~12 11~7 6~0 imm_i[11:0] rs1 111 rd 1010111 在rs1中计算AVL,将VL写回rd;

AVL:Application VL,实际要计算的向量长度;

imm_i符号扩展后描述VTYPE;

位 XLEN-1 XLEN-2:8 7 6 5 4:2 1:0 含义 vill(不当时取1) 0 vma vta vlmul[2] vsew[2:0] vlmul[1:0] vsew:向量一个元素的位数(汇编描述:e8、e16、…、e1024)

lmul使用向量寄存器的个数(汇编描述:m1、m2、m4、m8、mf8【1/8】、mf4【1/4】、mf2【1/2】)

VLMAX=VLEN x LMUL / SEW

vta规定如何处理tail元素,一般v0寄存器用作掩码寄存器(汇编描述:tu、ta)

vma用于考虑掩码(汇编描述:mu、ma)

eg.

vsetvli rd,rs1,e32,m2,ta,ma不考虑尾部元素和掩码C语言测试程序

GCC拓展汇编语法:

1

2

3

4

5

6asm("汇编语言"

:输出操作数

:输入操作数);

asm volatile("vsetvli %0,%1,e32,m1,tu,mu"

: "=r"(v1)

: "r" (size));其中r表示寄存器自动分配,=表示输出操作数,括号内为变量,再分别代入%0和%1中。

具体增加代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26常量:

val VREG_NUM = 32

val VLEN = 128

val CSR_VL = 0xC20.U(CSR_ADDR_LEN.W)

val CSR_VTYPE = 0xC21.U(CSR_ADDR_LEN.W)

val WB_VLI = 4.U(WB_LEN.W)

val CSR_V = 5.U(CSR_LEN.W) // vsetvli

译码:

VSETVLI-> List(ALU_NULL , OP1_NULL, OP2_NULL, MEM_NULL, REN_EN, WB_VLI ,CSR_V ),

访存+阶段:

//VSETVLI operation

val vtype = imm_i_sext

val vsew = vtype(4,2)

val vlmul = vtype(1,0)

val vlmax =((VLEN.U<<vlmul)>>(vsew+3.U(3.W))).asUInt()

val avl = rs1_data

val vl = MuxCase(0.U(WORD_LEN.W), Seq(

(avl <= vlmax) -> avl,

(avl > vlmax) -> vlmax

))

when(csr_cmd === CSR_V){

reg_csr(CSR_VL) := vl

reg_csr(CSR_VTYPE) := vtype

}

写回阶段:

(rd_sel === WB_VLI) -> vl

第二十八章 向量指令VLE

加载方式:unit-stride连续访问、stride相同间隔访问、indexed指定偏移序列访问

汇编描述:

vle8.v vd,(rs1)、vle16.v vd,(rs1)…vle64.v vd,(rs1)通过VLE指定的SEW(vle8、vle32…)成为EEW(effective element width),这样对加载不同SEW向量时节省了一条VSETVLI指令。同时EEW的改变导致LMUL改变,位EMUL。【EEW、EMUL再使用VWADD.WV等复杂指令时出现,简单指令可忽略和SEW、LMUL的差别】

位配置

31~29 28 27~26 25 24~20 19~15 14~12 11~7 6~0 nf mew mop vm lumop rs1 width vd 0000111 除vm、width均设为0;vm表示是否使用掩码(为1);width用于指定EEW

具体代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39val VLE = BitPat("b????_????_????_????_????_????_?000_0111")

val REN_VEC = 2.U(REN_LEN.W)

存储器增加接口:

val vrdata= Output(UInt((VLEN*LMUL_MAX).W))

core增加寄存器文件:

译码:

VLE -> List(ALU_COPY1 , OP1_RS1 , OP2_NULL, MEM_NULL, REN_VEC , WB_VLE , CSR_NULL),

写回阶段:

when(rd_wen === REN_EN){

reg_x(rd_addr) := rd_data

}.elsewhen(rd_wen === REN_LV){

val csr_vl = reg_csr(CSR_VL)

val csr_vsew = reg_csr(CSR_VTYPE)(4,2)

val sew = (1.u(1.W) << (csr_vsew + 3.U(3.W))).asUInt()

val data_len = csr_vl * sew

val last_addr = data_len / VLEN.U

for(i <- 0 to LMUL_MAX-1){

when(i < last_addr){

reg_vec(rd_addr + i.U) := rd_vdata((i+1)*VLEN-1, i*VLEN)

}.elsewhen(i === last_addr){

// tail-undisturbed

val remainder_len = data_len % VLEN.U

val tail_len = VLEN.U - remainder_len

val org_data = reg_vec(rd_addr + i.U)

val tail_data = ((org_data >> remainder_len) << remainder_len)(VLEN-1, 0)

val remainder_data = ((rd_vdata(VLEN*(i+1)-1,VLEN*i)<<tail_len)(VLEN-1,0)>>tail_len).asUInt()

val undisturbed_data = tail_data | remainder_data

reg_vec(rd_addr + i.U) := undisturbed_data

}

}

}

存储器读写:

def readData(len:Int) = Cat(Seq.tabulate(len/8)(n=>

mem(io.datamem.addr + n.U(WORD_LEN.W)).reverse

))

io.datamem.rdata := readData(WORD_LEN)

io.datamem.vrdata := readData(VLEN*LMUL_MAX)

涉及到tail元素的处理,使用undisturbed保留。

第二十九章 向量指令VADD.VV

位配置

vadd.vv vd,vs2,vs131~26 25 24~20 19~15 14~12 11~7 6~0 000000 vm vs2 vs1 000 vd 1010111 具体代码

1 | 常量: |

注:for循环会被展开转化,所以向量加法器本质是多个不同SEW位宽的向量加法器经过多路复用器选择计算结果。

第三十章 向量指令VSE

位配置

VSE8.V vs3,(rs1)、..VSE64.V vs3,(rs1)31~29 28 27~26 25 24~20 19~15 14~12 11~7 6~0 nf mew mop vm sumop rs1 width vs3 000111 具体代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29// memory write enable

val MEM_LEN = 3

val MEM_NULL = 0.U(MEM_LEN.W)

val MEM_EN = 1.U(MEM_LEN.W)

val MEM_VEC = 2.U(MEM_LEN.W)

Memory.scala:

val vwdata= Input(UInt((VLEN*LMUL_MAX).W))

val vlen = Input(UInt(WORD_LEN.W))

ID阶段:

val vs3_data = Cat(Seq.tabulate(LMUL_MAX)(i =>reg_vec(rd_addr + i.U)).reverse)

VSE -> List(ALU_COPY1 , OP1_RS1 , OP2_NULL, MEM_VEC , REN_NULL, WB_NULL, CSR_NULL),

MEM阶段:修改端口定义

val wen = Input(UInt(MEM_LEN.W))

switch(io.datamem.wen){

is(MEM_EN){

mem(io.datamem.addr) := io.datamem.wdata(7 , 0 )

mem(io.datamem.addr + 1.U(WORD_LEN.W)) := io.datamem.wdata(15, 8 )

mem(io.datamem.addr + 2.U(WORD_LEN.W)) := io.datamem.wdata(23, 16)

mem(io.datamem.addr + 3.U(WORD_LEN.W)) := io.datamem.wdata(31, 24)

}

is(MEM_VEC){

val byte_len = io.datamem.data_len/8.U

for(i <- 0 to VLEN-1){

when(i.U < byte_len){

mem(io.datamem.addr + i.U) := io.datamem.vwdata(i*8+7, i*8)

}

}

}

}

[3]手把手教你设计 CPU[^6]

第六章 蜂鸟 E200 流水线介绍

流水线反压——由于每一级流水线需要进行握手,流水线最后一级的反压信号可能会一直串扰到最前面一级

解决:取消握手(配合重执行【replay】、预留大缓存等机制)、加入乒乓缓存、加入前向旁路缓存

流水线冲突——资源冲突(例如运算单元中的除法器需要多个时钟周期);数据冲突(Tomasulo算法)(WAR和WAW通过寄存器重命名【register renaming】将相关性去除;RAW通过数据旁路传播技术【Data Bypass and Forward】或乱序发射队列追踪RAM相关性)

第七章 取指

快速取指

片外DDR存储器或FLASH存储器可能需要几十个存储周期的延迟,片上SRAM也可能要几个周期的延迟

通常使用ITCM和I-Cache方法:

- ITCM(Instruction Tightly Couple Memory)指令紧耦合存储器:小容量,离处理器核很近的专用存储器(通常SRAM),存放关键程序指令

- I-Cache(Instruction Cache)指令缓存:“将容量巨大的外部存储器空间动态映射到容量有限的指令缓存中”,不确定性(缓存不命中【Cache Miss】则需从外部存储器重新存取数据)

非对齐指令取指方法

- 对于普通指令:使用剩余缓存(Leftover Buffer),本次读取的32位指令只用到了16位,剩余16位存缓存与下一次的前16位拼接

- 分支跳转指令:多体(Bank)化SRAM存储指令,奇偶交错存储指令,一周期读两块SRAM拼接

分支指令的处理

分支指令分为:无条件直接/间接跳转(Unconditional Direct/Indirect Jump/Branch【jar/jalr】)、有条件直接/间接跳转(Conditional ~)

分支预测技术(Branch Prediction):预测取指(Speculative Fetch,预测“方向”和地址)和预测执行(Speculative Execution,对预取指令的执行)

“方向”预测

静态预测——不依赖曾经执行过的指令信息和历史信息,只依靠指令本身的信息进行预测。

- 总是预测分支不跳转

- BTFN预测(Back Taken,Forward Not Taken,向前预测不跳转,向后预测跳转)

动态预测——依赖曾经执行过的指令的历史信息和分支跳转指令本身信息进行预测。

两比特饱和计数器(n-bit saturating counter):强不需要跳转(strongly not taken)、弱不需要跳转(weekly

)、弱需要跳转(taken)、强需要跳转四种状态。

预测器表格(Predictor Table):每一条分支指令分配一个专有的饱和计数器,表格组织方式(大小)和索引方式(别名重合问题【Aliasing,有限表格对应大量分支指令必定产生索引重合】)

一级预测器:直接使用预测器表格,并使用PC的一部分进行索引其对应的两比特饱和计数器,使用其计数器进行预测,最终跳转的结果作为计数器更新的输入。但是索引机制过于简单,且未考虑分支指令的上下文执行历史,精度不如二级预测器。

两级预测器(相关预测器【Correlation-Based Branch Predictor】):通过PC索引该分支跳转指令的跳转历史,然后使用n-bit的分支跳转历史(Branch History)作为索引,将2^n个两比特饱和计数器组织成PHT(Pattern History Table),考虑了分支指令的历史跳转信息;不是将PC作为索引,而是n-bit的历史,进而构建起跳转模式。

[^18]

[^18]- “New Algorithm Improves Branch Prediction: 3/27/95” (PDF). Microprocessor Report. 9 (4). March 27, 1995. Archived (PDF) from the original on 2015-03-10. Retrieved 2016-02-02.

局部分支历史(Local History)、局部预测器(Local Branch Predictor)和全局历史(Global ~,所有分支指令的跳转历史)、全局预测器——全局分支预测算法GShare和Gselect(索引方式不同)

“地址”预测

- BTB(Branch Target Buffer,分支目标缓存):记录分支指令PC值及其跳转地址

- RAS(Return Address Stack,返回地址堆栈):调用函数时压栈返回地址(PC+4),返回时直接出栈作为预测地址。

- Indirect BTB:“存储较多历史目标地址,通过高级索引方式进行匹配,可以说是结合了BTB和动态两级预测器的计数”[^6]

预测错误的措施

- 流水线冲刷(Flush Pipeline)

- 分支延迟槽(Delay Slot,不使用Bubble而是在跳转指令后紧跟必须执行的指令,进而不浪费性能【早期MIPS架构】)

指令长度识别码[^13]

(RISC-V架构中的16位压缩指令集的指令和64位指令集可对应到32位的等效指令)

提供明确的RAS依据

RISC-V架构中明确规定,如果使用jal指令且目标寄存器值rd等于x1或者x5,则需要进行RAS压栈;如果使用jalr指令,则按照使用的寄存器值(rs1和rd)的不同,明确规定了相应的RAS压栈或出栈行为。

[^13]

第14章 调试

- JTAG协议传入SoC解析,硬件支持

相关论文

[1]RISC-V架构的开源处理器及SoC研究综述[^7]

简单介绍了加州大学伯克利分校(UniversityofCali—forniaatBerkeley,以下简称UCB)的Rocke、BOOM、sodor等开源处理器所支持的指令集包括基础指令集和扩展指令集两类,如RV32I、RV64G和流水线等配置,并将性能与ARM或X86同类型的处理器进行对比;以及介绍了Rocket-Chip等开源SOC。

[2]RISC-V指令集架构研究综述[^8]

前言从RISC-V出现的原因,并与X86,ARM指令集进行了对比(开放、精简、独立、可定制、可拓展);对指令集ISA进行了解释与理解(规定硬件设计的功能目标,对硬件能力的抽象);对于RISC-V指令集的研究包括硬件实现、指令集自身、上层系统和应用

***<1>***RISC-V ISA

1. RV32I/RV64I整数指令集使用32个通用REG和一个特殊REG(PC),位宽XLEN不同,x0 寄存器的所有位都被硬布线为 0 值。其他寄存器具体作用如下:

- RV32I 有四种指令格式:R/I/S/U,指令集中的任何指令都可以根据操作数的数量、种类、规模以及自身的功能需求(如ADDRI/ADDR/ADDS/ADDU),选用其中一种格式.所有这些指令格式都是 32 位固定长度,并且必须在内存中对齐到 4 字节的边界;

- RV64I 采用与 RV32I 相同的指令格式,只是将整数寄存器和所支持的用户地址空间扩展到了 64 位,增加了一些操作低 32 位的***“*W”指令***;

- RV32E 是对 RV32I 指令集的一种简化,将可用的整数寄存器的数目从 32 减少到 16,即只使用 x0~x15 和 pc 完成所有的指令功能(调用约定和ABI(application binary interface,应用程序二进制接口)与RV32I不兼容);

- RV128I是对 RV32I 和 RV64I 的直接外扩,仅仅是把整数寄存器宽度扩展到了 128 位(XLEN=128).由于大部分整数运算指令在 XLEN 位上定义,所以无需变化.此外,RV128I 保留了 RV64I 中用于操作低 32 位的“*W”指令,只是把结果从 32 位符号扩展到 128 位;RV128I 还新增了用于操作低 64 位的“*D”指令.

- RVWMO:内存一致性模型?

上面图源:[?]Waterman A, Asanovic K. The RISC-V Instruction Set Manual, Volume I: Unprivileged ISA. Vol. 1. SiFive Inc., 2021.

- 拓展指令集…

- RISC-V权限规范:机器模式(Machine,M 模式,所有权限,必须实现)、用户模式(User,U 模式,最低级别)、管理模式(Supervisor,S 模式)、监视模式(Hypervisor,H 模式).其中,H 模式暂时处于草案状态

***<2>***RISC-V硬件平台

- 处理器设计:

- 处理器和模拟器方面的主要研究成果:

图源:[?]riscvarchieve. RISC-V Cores and SoC Overview. 2021. https://github.com/riscvarchive/riscv-cores-list

模拟器是在软件层面对底层硬件平台或其他软件环境进行模拟的工具.它允许开发人员在非目标硬件设备上获得与目标硬件设备相同或相似的体验,简化研发流程,并有助于提前发现开发中的问题.例如,在 RISC-V平台中使用 QEMU 模拟器运行 Linux 操作系统就是一种很常见的做法。

***<3>***RISC-V系统设计

多处理器系统和处理器集群系统未看

***<4>***测试与验证

在系统设计的任何一个环节都需要有与之对应的测试或验证方法来保障其正确性(sail、secchisel、serval等[*尚不清晰具体作用*])

***<5>***RISC-V系统性能优化

最主要的优化需求集中在处理器、内存、通信、能耗 4 个方面。(对 RISC-V 系统性能优化的思路和有关成果详述见原论文)

***<6>***RISC-V系统安全策略设计

系统可能遭受的安全威胁:硬件微架构攻击、内存攻击、侧信道攻击(side channel attack,简称 SCA).(具体攻击示例见原文,如系统供应链的微码木马和缓冲区溢出攻击等)

***<7>***RISC-V应用场景分析

***<8>***RISC-V未来发展趋势

硬件新发展方向(硬件异构解决方案)、与新技术结合(如脑机接口通用架构HALO)

[3]RISC-V手册[^9]

全书目录:RISC-V简介、RV32I、RISC-V汇编、RV32G、乘除法RV32M、浮点操作RV32F/RV32D、原子操作RV32A、压缩拓展RV32C、向量拓展RV32V、RV64G、RV32/64特权架构、RISC-V未来拓展

***<1>***RISC-V设计目标

- 通用ISA(它应该对所有微体系结构样式都有效:例如微编码或硬连线控制;顺序或乱序执行流水线; 单发射或超标量等等;支持专业化[定制加速器];适用所有实现技术……);是****模块化ISA*(区别于增量型ISA[如X86向前兼容]),核心是一个名为RV32I的基础ISA;特性为简洁性(与ARM和X86对比),简单的*指令组合*来实现复杂功能并提升性能(更快的时钟频率或更低的平均单条指令周期数[CPI]);提升空间(保留操作码空间以供未来的提升或自定义指令);程序大小更小(X86虽然使用可变字节长度指令,但有着一到两个字节长前缀的负担,迫使它们使用原始 x86 的有限的空余操作码空间);易于编程/编译/链接(*寄存器更多****[32],每条指令最多1个时钟周期)

*<2>*RV32I[^13]

- *六种基本指令格式*:用于****寄存器-寄存器操作****的 ****R 类型*指令,用于*短立即数和访存 load 操作****的 ****I 型*指令,用于*访存 store 操作****的 ****S 型*指令,用于*条件跳转****操作的 ****B 类型*指令,用于*长立即数****的 ****U 型*指令和用于*无条件跳转****的 ****J 型****指令。

RISC-V 将立即数中的位从自然排布进行了一些移位轮换,将指令信号的扇出和立即数多路复用的成本降低了近两倍,这也简化了低端实现中的数据通路逻辑.(ARM-32 指令集 12 位的立即字的8 位被零扩展到全宽度,然后被循环右移剩余 4 位的值乘 2。这些条件执行指令不仅使用频率低而且增加了乱序处理器的复杂性。);即使处理器没有添加乘除法扩展,完整的 RISC-V 软件栈也可以运行;load和store指令的支持的唯一寻址模式是符号扩展 12 位立即数到基地址寄存器(RV32I *省略*了 ARM-32 和 x86-32 的*复杂寻址模式*,且****没有特殊的堆栈指令*);支持内存数据*不对齐访问****;条件分支指令的寻址方式是 12 位的立即数乘以 2,符号扩展它,然后将得到值加到PC 上作为分支的跳转地址(bltu 允许使用单个指令检查有符号数组的边界[任何负索引都将比任何非负边界更大])

指令组合实现功能的汇编示例(大位宽数据的加法[sltu 计算进位]、获取 PC[auipc 的 U 立即数字段设置为 0 来获得]、软件检查溢出[addu t0,t1,t2; bltu t0,t1,overflow])

其他指令:*控制状态寄存器指令(csrrc、csrrs…)*;ecall;fence;系统指令…RISC-V 使用****内存映射I / O*而不是像x86-32一样,使用 in,out,等指令;为支持字符串处理,RISC-V 实现了*字节存取****,而不是像 x86-32 那样实现了 rep,movs等特殊的字符串处理指令。

使用指令图[^12]表示:(具体使用见附录A)

- RV32I寄存器:x0

x31+PC,*PC另作为一个特殊寄存器*,其中x0x31使用应用程序二进制接口(ABI)所定义的寄存器名称见下。(x0:为常量 0 单独分配一个寄存器是 RISC-V ISA 能如此简单的一个很大的因素,可以****用零寄存器作为操作数完成功能相同的操作*)(*PC 作为一个寄存器使硬件分支预测变得复杂****,任何改变寄存器的指令都可能导致分支跳转,且通用寄存器少一个)

- 相关特性(其他改进见****P37****):

***<3>***RISC-V汇编语言

*函数调用规范*(6阶段):

- 将参数存储到函数能够访问到的位置;

- 跳转到函数开始位置(使用 RV32I 的 jal 指令);

- 获取函数需要的局部存储资源,按需保存寄存器;

- 执行函数中的指令;

- 将返回值存储到调用者能够访问到的位置,恢复寄存器,释放局部存储资源;

- 返回调用函数的位置(使用 ret 指令)。

RISC-V 有够多的寄存器能将操作数存放在寄存器中****同时也能减少保存和恢复寄存器的次数。*在函数调用的时不保留部分寄存器存储的值的为*临时寄存器*;反之为*保存寄存器*。(频繁地保存和恢复寄存器会*访问内存降低性能****)

- 标准的 RV32I *函数入口和出口*:

- 汇编器:汇编指示符(汇编器命令,告诉汇编器代码和数据的位置、指定程序中使用的特定代码和数据常量等):

- 伪指令:

- *链接器*:链接器允许各个文件独立地进行编译和汇编;除了指令,每个目标文件还包含一个符号表,存储了程序中标签,由链接过程确定地址。其中包括了数据标签和代码标签(数据标签需要调整 lui和 addi,代码标签需要调整 auipc 和 jalr);RISC-V 编译器支持多个 ABI,ilp32,ilp32f 和 ilp32d(ilp32 表示 C 语言的整型(int),长整型(long)和指针(pointer)都是 32 位,可选后****缀表示如何传递浮点参数*。在 lip32 中,浮点参数在整数寄存器中传递;在 ilp32f 中,单精度浮点参数在浮点寄存器中传递;在 ilp32d 中,双精度浮点参数也在浮点寄存器中传递。);如果想在浮点寄存中传递浮点参数,需要相应的浮点 ISA 添加 F 或 D 扩展(见第 5 章)。因此要编译 RV32I 的代码*(GCC 选项-march=rv32i)*,*必须使用 ilp32 ABI(GCC选项-mabi=lib32)****。反过来,调用约定并不要求浮点指令一定要使用浮点寄存器,因此RV32IFD 与 ilp32,ilp32f 和 ilp32d 都兼容。链接器检查程序的 ABI 是否和库匹配。

***<4>***RISC-V特权架构[^14]

- 我们引入的所有指令都在用户模式(应用程序的代码在此模式下运行)下可用;除此之外,运行最可信的代码的机器模式(machine mode),以及为 Linux,FreeBSD 和 Windows 等操作系统提供支持的监管者模式(supervisor mode)。嵌入式系统运行时(runtime)和操作系统用新模式的功能来响应外部事件,如网络数据包的到达;支持多任务处理和任务间保护;抽象和虚拟化硬件功能等。

- 机器模式M:是 RISC-V 中 hart(hardware thread,硬件线程)可以执行的最高权限模式。在 M 模式下运行的 hart 对内存,I/O 和一些对于启动和配置系统来说必要的底层功能有着完全的使用权。因此它是唯一所有标准 RISC-V 处理器都必须实现的权限模式;最重要的特性是****拦截和处理异常****(不寻常的运行时事件)的能力;一类是同步异常,这类异常在指令执行期间产生,如访问了无效的存储器地址或执行了具有无效操作码的指令时,另一类是中断,它是与指令流异步的外部事件。同步异常如下:

三种标准的中断源:软件、时钟和外部来源。软件中断通过向内存映射寄存器中存数来触发;当 hart 的时间比较器(一个名为 mtimecmp 的内存映射寄存器)大于实时计数器mtime 时,会触发时钟中断;外部中断由平台级中断控制器(大多数外部设备连接到这个中断控制器)引发。

****机器模式下的异常处理:****处理器在M模式下运行,只有在全局中断使能位 mstatus.MIE 置 1 时才会产生中断.此外,每个中断在控制状态寄存器 mie 中都有自己的使能位。这些位在 mie 中的位置对应于中断码exception code。

用户模式(U模式)拒绝使用这些功能,并在尝试执行 M 模式指令或访问 CSR 的时候产生非法指令异常。通过将 mstatus.MPP 设置为 U(如图 10.5 所示,编码为 0)。如果在U模式下发生异常,则把控制移交给 M 模式。物理内存保护(PMP,Physical Memory Protection)功能允许M模式指定U模式可以访问的内存地址[但 PMP 仅支持固定数量的内存区域,因此无法对它进行扩展从而适应复杂的应用程序]。

监管者模式(S模式):使用基于页面的虚拟内存,这构成了S模式的核心;S 模式的中断和异常会进行系统调用,RISC-V 提供了一种异常委托机制,可以选择性地将中断和同步异常交给 S 模式处理,而完全绕过 M 模式(S 模式异常将会移交 S 模式的异常处理程序,而不是 M 模式的异常处理程序)(S 模式不直接控制时钟中断和软件中断,而是使用 ecall 指令请求 M模式设置定时器或代表它发送处理器间中断。)。通过mideleg(Machine Interrupt Delegation,机器中断委托)CSR、sie、sip、sstatus等CSR;页表项SvX见手册,satp(Supervisor Address Translation and Protection,监管者地址转换和保护)的 S 模式控制状态寄存器控制了分页系统。用地址转换缓存(通常称为 TLB,全称为 Translation Lookaside Buffer)来减少访存开销,sfence.vma 会通知处理器,可能修改了页表以刷新转换缓存。

- RISC-V 特权架构的模块化特性满足了各种系统的需求。十分精简的机器模式以低成本的特征支持裸机嵌入式应用。附加的用户模式和物理内存保护功能共同支持了更复杂的嵌入式系统中的多任务处理。最后,监管者模式和基于页面的虚拟内存提供了运行现代操作系统所必需的灵活性。

[4]芯片敏捷开发实践:标签化RISC-V[^10]

这份文件是《芯片敏捷开发实践:标签化RISC-V》,主要介绍了Chisel语言在RISC-V处理器敏捷开发中的应用及其优越性。以下是具体内容:

1. *Chisel语言简介*:

1. *硬件描述语言*:Chisel是一种构建在Scala语言之上的硬件描述语言,专门用于简化复杂数字硬件的设计和实现。

2. *抽象层次高*:相比传统的硬件描述语言(如Verilog和VHDL),Chisel提供了更高的抽象层次,使得设计者能够更加关注于算法和架构,而不是底层的实现细节。

2. *Chisel在RISC-V开发中的应用*:

1. *敏捷开发*:利用Chisel语言,开发者能够更快速地实现RISC-V处理器的各种功能,从而加速开发过程。

2. *模块化设计*:Chisel支持模块化设计,使得RISC-V处理器的各个组件可以独立开发、测试和集成,提高了开发效率和代码的可维护性。

3. *研究结果*:

1. *提高开发效率*:通过实际项目验证,使用Chisel开发RISC-V处理器的效率相比传统方法提高了约30%。

2. *减少错误率*:Chisel的高层次抽象和类型检查机制有效减少了设计错误,提高了代码的正确性和可靠性。

4. *相关数据*:

1. *项目周期缩短*:某RISC-V处理器开发项目在使用Chisel后,项目周期缩短了约两个月。

2. *代码行数减少*:相比使用传统硬件描述语言,使用Chisel实现的RISC-V处理器代码行数减少了约20%。

5. *研究方法*:

1. *对比实验*:通过对比使用Chisel和传统硬件描述语言开发RISC-V处理器的过程,评估Chisel的优越性和效率。

2. *案例分析*:选取典型的RISC-V处理器开发项目,分析使用Chisel前后的开发效率、代码质量和维护成本等指标。

6. *Chisel的优越性*:

1. *高层次抽象*:Chisel提供了更高的抽象层次,使得设计者能够更加关注于算法和架构,简化了设计过程。

2. *模块化设计*:支持模块化设计,提高了代码的可重用性和可维护性。

3. *类型检查*:Chisel的类型检查机制有效减少了设计错误,提高了代码的正确性。

4. *集成开发工具*:Chisel与Scala生态系统中的其他工具集成良好,提供了丰富的开发、测试和调试功能。

总结: 该文献通过实际项目验证了Chisel语言在RISC-V处理器敏捷开发中的优越性,包括提高开发效率、减少错误率、缩短项目周期和降低维护成本等方面。Chisel的高层次抽象、模块化设计、类型检查和集成开发工具等特点使得它成为RISC-V处理器开发的理想选择。

[5]基于RISC-V的五级流水线处理器的设计与研究[^11]

静态分支预测SOC设计

有关论文结构的学习——研究现状、基础知识概要、个人设计验证…

关键词

在“取指”单元设计中,指令寄存器采用了指令耦合寄存器设计, 保证了“快速”取指,同时采用分支预测设计,有效避免了条件跳转指令造成的 流水线冲刷而带来的性能丢失;“执行”单元针对流水线存在的WAW和RAW两 种数据相关性而设计了旁路电路模块;“访存”单元设计增加访存控制信号,判 断是否需要暂停,从而提高硬件模块的利用率和吞吐率。

在取指阶段可加入静态指令预测器;旁路单元即branch;在执行和访存阶段可加入乘除法器;在访存阶段可加入总线接口

在是对分支跳转指令进行“方向”和“目标地址”的预测,动静态分支预测

流水线冲突冒险,在流水线结构上加“支流”

第二章相关研究部分大量使用流水线、其他soc结构、总线通信协议等充量;第三章按5级流水分别具体介绍;第四章SOC部分具体介绍总线外挂外设的通信协议;由于其各阶段部件独立,综合后按模块分布。仿真测试先按阶段给出波形图,然后大量使用部件的具体结构和仿真充量

[6]处理器流水线冒险及其解决策略^17

开源处理器

[1]Rocket Chip Generator[^12]

处理器结构

从图中可以看出,Rocket-Chip项目有六个组成部分:

- A为Core Generator,用于生成处理器核,支持Rocket-core和BOOM两种

- B为Cache,包括L1 Cache和L2 Cache

- C为RoCC,即Rocket的用户自定义加速器接口,用户可以使用Chisel自行编写加速器挂载到Rocket-chip中

- D为Tile,一个处理器核和一个L1 Cache(包括指令Cache和数据Cache)构成一个Tile,在Rocket-chip中通过复用各种Tile构建一个多核(同构或异构)的体系

- E为TileLink,为UC Berkeley自行开发的片上总线,用于连接处理器、缓存和外设

- F为Peripheral,包括AMBA兼容总线(AXI,AHB-Lite和APB)的发生器以及各种转换器和控制器。

主要资源清单

Rocket Chip工程目录- bootrom —包含第一阶段bootloader的源代码。

- docs —代码库特定部分的文档、教程等。

- emulator —编译和运行Verilator仿真的目录。

- src\main\resources\csrc —用于Verilator仿真的C源代码。

- regression —定义连续集成和nightly regression套件。

- scripts —用于解析模拟输出或操作源文件内容的实用程序。

- vsim —编译和运行Synopsys VCS仿真的目录。

- src\main\resources\vsrc —包含interfaces、harnesses 和 VPI的Verilog源。

1、

src\main\scala目录:该目录包含两种类型的模块:①一种是工具utility,类似helper性质,用来帮助代码实现,并不直接生成硬件。如:

- config —此实用程序包提供Scala接口,用于通过动态查找的参数化库配置生成器。

- diplomacy —此实用程序包通过允许

two-phase hardware elaboration(双相硬件精化)扩展了Chisel,其中某些参数在模块之间动态协商。diplomacy是一种用于高级参数化的机制:它实现了模块之间的参数协商,参数在模块之间传递时可以根据需求协商与检查,更加灵活且不容易出错;还可以快速实现设计拓扑的参数化,使用verilog实现设计拓扑的参数化是非常困难的一件事,往往包含着大量的define,容易出错,且写起来困难。有关diplomacy的更多信息,请参阅 这篇文章。 - regmapper —该实用程序包生成具有标准化接口的从设备,用于访问其内存映射寄存器。

- system —调用其他各种模块,构造可配置的系统。

- unittest —可综合的单元测试代码的框架。注意,这与Chisel的tester框架完全不同。

②另一种是硬件模块的生成器。如:

- amba —这个RTL包使用diplomacy机制生成AMBA协议的总线实现,包括AXI4、AHB lite和APB。

- devices —这个RTL包包含了各种外设的实现,它包括调试模块和各种TL(UC Berkeley自己开发的片上总线协议)从机(外设做从机)。

- groundtest —这个RTL包生成可综合的硬件测试器,这些测试器发出随机内存访问流,以便对非核心内存层次结构进行压力测试。

- interrupts —使用diplomacy实现的中断逻辑。

- jtag —这个RTL包提供了生成JTAG总线接口的定义。

- rocket —该RTL包生成Rocket的 in-order 流水线内核、L1指令和数据缓存、FPU、RoCC协处理器等。

- scie —用于在core流水线里面添加自定义指令的接口。

- subsystem —公共总线架构的实现,包含master和slave接口。它包含了一些系统中经常需要添加的模块,用户自己创建系统时可以继承该子系统实现复用,这样只需要再手动添加其他模块即可。

- tile —可以包含

core,FPU,L1缓存,RoCC协处理器等的容器。在Rocket-chip中通过复用各种Tile构建一个多核(同构或异构)的系统。 - tilelink —这个RTL包使用diplomacy机制生成TileLink协议的总线实现。它还包含各种适配器和协议转换器。

- util —此实用程序包提供了多种常见的Scala和Chisel编写的程序,可在多个其他包中被重复使用。如一些常见逻辑,ECC,arbiter, mux,随机数生成器等。

Other Resources

Outside of Scala, we also provide a variety of resources to create a complete SoC implementation and test the generated designs.

- bootrom Sources for the first-stage bootloader included in the BootROM.

- csrc C sources for use with Verilator simulation.

- docs Documentation, tutorials, etc for specific parts of the codebase.

- emulator Directory in which Verilator simulations are compiled and run.

- regression Defines continuous integration and nightly regression suites.

- scripts Utilities for parsing the output of simulations or manipulating the contents of source files.

- vsim Directory in which Synopsys VCS simulations are compiled and run.

- vsrc Verilog sources containing interfaces, harnesses and VPI.

RooketCore代码

构建标志位

RocketCoreParams通过设置里面的参数更改处理器配置如

xLen: Int = 64,、useSupervisor: Boolean = false,等,生成最终的Verilog处理器IO

Rocket处理器IO配置类

HasRocketCoreIO中将处理器通过特定IO口如val fpu = Flipped(new FPUCoreIO())与其它部件连接。主要部分

Rocket类在

val decode_table中根据配置选择具体的译码器类型如I32Decode、I64Decode、HypervisorDecode等,在IDecode.Scala中定义直接在主体部分定义各阶段流水线寄存器:

1

2

3

4

5

6

7

8val ex_reg_xcpt_interrupt = Reg(Bool())

val ex_reg_valid = Reg(Bool())

val ex_reg_rvc = Reg(Bool())

...

val mem_reg_xcpt_interrupt = Reg(Bool())

...

val wb_reg_valid = Reg(Bool())

...译码阶段

连接译码模块信号、处理信号。前面提到在

IDecode.Scala中定义译码器,其中的实现方式是直接进行指令译码:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17class IDecode(implicit val p: Parameters) extends DecodeConstants

{

val table: Array[(BitPat, List[BitPat])] = Array(

BNE-> List(Y,N,N,Y,N,N,Y,Y,A2_RS2, A1_RS1, IMM_SB,DW_XPR,FN_SNE, N,M_X, N,N,N,N,N,N,N,CSR.N,N,N,N,N),

...

```scala

5. 执行阶段

rocket选择在ex阶段得到一二操作数ex_op1和ex_op2。然后在rocket内直接新建了一个alu模块和除法器div模块:

```scala

val alu = Module(new ALU)

alu.io.dw := ex_ctrl.alu_dw

alu.io.fn := ex_ctrl.alu_fn

alu.io.in2 := ex_op2.asUInt

alu.io.in1 := ex_op1.asUInt寄存器文件的封装

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25class RegFile(n: Int, w: Int, zero: Boolean = false) {

val rf = Mem(n, UInt(w.W))

private def access(addr: UInt) = rf(~addr(log2Up(n)-1,0))

private val reads = ArrayBuffer[(UInt,UInt)]()

private var canRead = true

def read(addr: UInt) = {

require(canRead)

reads += addr -> Wire(UInt())

reads.last._2 := Mux(zero.B && addr === 0.U, 0.U, access(addr))

reads.last._2

}

def write(addr: UInt, data: UInt) = {

canRead = false

when (addr =/= 0.U) {

access(addr) := data